# **Chapter 2**

# **Transistor Biasing**

## **CHAPTER HIGHLIGHTS**

- IN The Operating Point

- Bias Stability

- Biasing the BJT

- Bias Compensation

- Thermistor Compensation

- Sensistor Compensation

- 🖙 Thermal Run Away

- Thermal Resistance

- 🖙 Heat Sink

- Biasing the FET

## THE OPERATING POINT

A transistor is a current-controlled three-terminal device having two junctions, namely base–emitter junction and base–collector junction

| Base—emitter<br>junction | Base-collector<br>junction | Application | Region of operation |

|--------------------------|----------------------------|-------------|---------------------|

| FB                       | FB                         | ON switch   | Saturation          |

| FB                       | RB                         | Amplifier   | Active              |

| RB                       | FB                         | -           | Inverse active      |

| RB                       | RB                         | OFF switch  | Cut-off             |

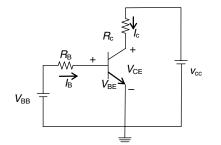

## **Transistor Circuit Under DC Condition**

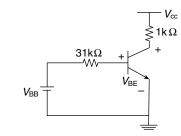

Apply KVL at input side gives  $V_{BB} - I_B R_B - V_{BE} = 0$

$\Rightarrow V_{\rm BE} = V_{\rm BB} - I_{\rm B}R_{\rm B}$

When

$$I_{\rm B} = 0 \Longrightarrow V_{\rm BE} = V_{\rm BB}$$

$V_{\rm BE} = 0 \Longrightarrow I_{\rm B} = \frac{V_{\rm BB}}{R}$

DC load line is the line joining the two points.

$$(V_{\rm BB}, 0)$$

and  $\left(0, \frac{V_{\rm BB}}{R_{\rm B}}\right)$

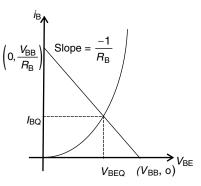

## Input Characteristics of CE Transistor

Intersection of the load line with the characteristics of the transistor gives the Q point (operating point)

Apply KVL at the output.

$$V_{\rm CC} - I_{\rm C} R_{\rm C} - V_{\rm CE} = 0$$

$$V_{\rm CE} = 0 \Rightarrow I_{\rm C} = \frac{V_{\rm CC}}{R_{\rm C}}$$

$$I_{\rm C} = 0 \Longrightarrow V_{\rm CE} = V_{\rm CC}$$

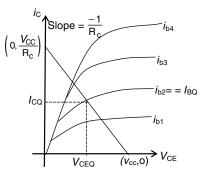

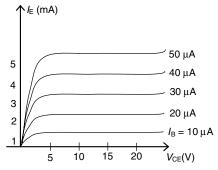

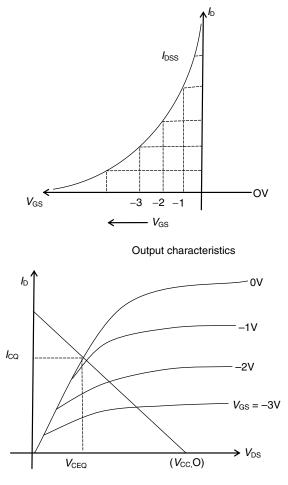

## **Output Characteristics of a CE Transistor**

#### 3.466 | Part III • Unit 5 • Analog Circuits

Intersection of the load line with the output characteristics for a particular value of  $I_{\rm B}$  gives the Quiscent point/ operating point.

Hence, 'Q' point is given by  $Q(I_{CO}, V_{CEO})$

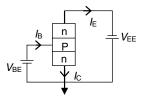

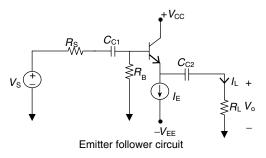

#### **Common Collector Amplifier**

This is also known as emitter follower. This configuration mainly used for impedance matching because of it's highinput impedance and low-output impedance.

Notation of common collector configuration.

Output characteristics of common collector configuration are a plot of emitter current  $I_{\rm E}$  versus  $V_{\rm CE}$  for a range of  $I_{\rm B}$

Output characteristics of common emitter configuration.

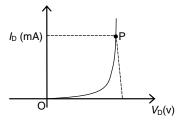

#### Static and Dynamic Resistance

DC (or) static resistance.

Operating point (Q) will not change with time if input voltage is DC.

DC resistance is the ratio of voltage to current at operating point.

At point P,

$$R_{\rm D} = \frac{V_D}{I_D}$$

DC resistance is independent of the shape of characteristic surrounded by the point.

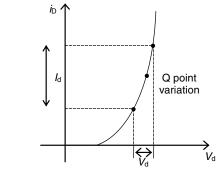

#### AC (or) Dynamic Resistance

If input is sinusoidal signal, then operating point moves up and down and thus gives a specific change in current and voltage.

AC resistance

$$r_{\rm d} = \frac{\Delta V_d}{\Delta I_d}$$

#### **Solved Examples**

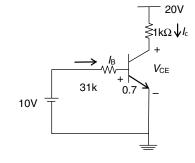

#### Example 1

Determine the 'Q' point for the following circuit if  $\beta = 50$ and  $V_{BB} = 10$  volts,  $V_{BE} = 0.7$  volts,  $V_{CC} = 20$  volts

(A) (0.3 mA, 5 V)

(B) (15 mA, 5 V)

(C) (0.6 mA, 4 V)

(D) (15 mA, 4 V)

#### Solution

Writing KVL for the base emitter loop gives

$$10 - 31 I_{\rm B} - 0.7 = 0$$

$$\Rightarrow I_{\rm B} = 0.3 \text{ mA}$$

$$I_{\rm CQ} = \beta (0.3 \text{ mA}) = 15 \text{ mA}$$

Writing KVL for the collector loop gives

$$20V - I_{\rm C} (1 \text{ k}\Omega) - V_{\rm CE} = 0$$

$$\Rightarrow V_{\rm CE} = 20 - (15 \text{ mA}) (1 \text{ k})$$

$$= 20 - 15$$

$$V_{\rm CE} = 5 \text{ Volts}$$

$$(I_{\rm C}, V_{\rm CEO}) = (15 \text{ mA}, 5 \text{ V})$$

## **BIAS STABILITY**

Operating point defines where the transistor will operate on its characteristics curve, under DC conditions. For linear (minimum distortion) amplification, the DC operating point should not be too close to the maximum power and voltage or current rating and should avoid the regions of saturation and cut-off. To keep the operating point stable, we use external network to bias the transistor.

The stability of operating point depends on  $V_{\rm BE}$ ,  $\beta$ ,  $I_{\rm CO}$ .  $\beta$  is very sensitive to temperature, and  $V_{\rm BE}$  decreases about 2.5 mV for each 1°C increase in temperature. The reverse saturation current typically doubles for every 10°C increase is temperature.

#### **Stability Factor (S)**

$$I_{\rm C} = f(I_{\rm CO}, V_{\rm BE} \beta)$$

$$S = \frac{\partial I_{\rm C}}{\partial I_{\rm CO}}, S^{\rm I} = \frac{\partial I_{\rm C}}{\partial V_{\rm BE}} \cdot S^{\rm II} = \frac{\partial I_{\rm C}}{\partial \beta}$$

$$I_{\rm C} = \beta I_{\rm B} + (1 + \beta) I_{\rm CO}$$

Differentiating with respect to  $I_C$  gives

$$I = \beta \frac{\partial I_{\rm B}}{\partial I_{\rm C}} + (1 + \beta) \frac{\partial I_{\rm CO}}{\partial I_{\rm C}}$$

$$\Rightarrow 1 = \beta \frac{\partial I_{\rm B}}{\partial I_{\rm C}} + \frac{1 + \beta}{S}$$

$$\Rightarrow S = \frac{1 + \beta}{1 - \beta \frac{\partial I_{\rm B}}{\partial I_{\rm C}}}$$

Where 'S' is the stability factor

Smaller value of 'S' is desirable for a proper biasing of circuit to act as an amplifier.

The networks are the most stable and least sensitive to temperature changes have the smallest stability factors

## BIASING THE BIPOLAR JUNCTION TRANSISTOR (BJT)

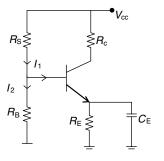

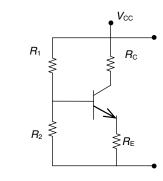

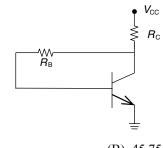

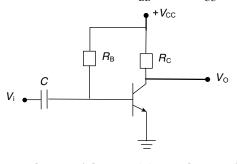

## **Base Bias or Fixed Bias**

Input loop

$$V_{\rm CC} = I_{\rm B} R_{\rm B} + V_{\rm BE}$$

$$I_{\rm b} = \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm B}}$$

$$R_{\rm B}$$

Output loop

$$V_{\rm CC} - I_{\rm C} R_{\rm C} - V_{\rm CE} = 0$$

$$V_{\rm CE} = V_{\rm CC} - I_{\rm C} R_{\rm C}$$

$$I_{\rm C} = \beta I_{\rm b} = \beta \left( \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm b}} \right)$$

Voltage drop across  $R_{\rm C}$  can never be greater than  $V_{\rm CC}$ .

$$I_{\rm C} R_{\rm C} < V_{\rm CC} \Rightarrow I_{\rm C} < \frac{V_{\rm CC}}{R_{\rm C}}$$

If  $I_{\rm C}$  becomes greater than this value, the operating point will lie in saturation region,.

Stability factor =

$$S = 1 + \beta$$

$\left( \because \frac{\partial I_{\rm B}}{\partial I_{\rm C}} = 0 \right)$

It is a simple circuit with few parts.

Operating point can be fixed anywhere in active region, by simply varying  $R_{\rm p}$

$I_{\rm C}$  depends on  $\beta$ ,  $\overline{\beta}$  in turn unstable with respect to temperature, this biasing in useful is switching and digital applications.

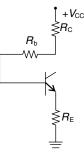

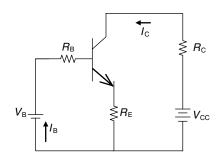

#### **Collector-to-Base Bias Circuit**

Input loop

$$V_{\rm CC} - (I_{\rm B} + I_{\rm C}) R_{\rm C} - R_{\rm b} I_{\rm B} - V_{\rm BE} = 0$$

$$\Rightarrow \frac{\partial I_{\rm B}}{\partial I_{\rm C}} = \frac{-R_{\rm C}}{R_{\rm C} + R_{\rm B}}$$

$$I_{\rm b} = \frac{I_{\rm C}}{\beta}$$

$$\Rightarrow I_{\rm B} = \frac{V_{\rm CC} - V_{\rm BE}}{(\beta + 1)R_{\rm C} + R_{\rm B}}$$

$$\therefore I_{\rm C} = \frac{\beta(V_{\rm CC} - V_{\rm BE})}{(\beta + 1)R_{\rm C} + R_{\rm B}}$$

If ' $\beta$ ' is very large ( $I_{\rm B} = 0$ ), then the approximate value of

$$I_{\rm C} = \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm C}}$$

KVL at output side:

$$V_{\rm CC} - (I_{\rm C} + I_{\rm B}) R_{\rm C} - V_{\rm CE} = 0$$

$$\Rightarrow V_{\rm CE} = V_{\rm CC} - (I_{\rm C} + I_{\rm B}) R_{\rm C}$$

If  $(\beta + 1) R_{\rm C} >> R_{\rm B}$ , then  $I_{\rm C} = \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm B}}$  independent of ' $\beta$ '

The feedback resistor  $R_{\rm B}$  provides negative feedback for AC input consequently reduces the AC gain of the circuit.

Stability factor

$$S = \frac{1+\beta}{1+\beta\left(\frac{R_{\rm C}}{R_{\rm C}+R_{\rm B}}\right)}$$

Collector to base bias is having lesser stability factor than fixed bias. Thus, it provides better stability.

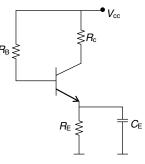

#### **Emitter Feedback Bias**

$$I_{\rm E} = I_{\rm C} + I_{\rm B}$$

$$V_{\rm E} = I_{\rm E} R_{\rm E} = (I_{\rm C} + I_{\rm B}) R_{\rm E}$$

$$V_{\rm B} = V_{\rm BE} + (I_{\rm C} + I_{\rm B}) R_{\rm E}$$

$$I_{\rm B} = \frac{V_{\rm CC} - V_{\rm B}}{R_{\rm b}}$$

$$R_{\rm E} \downarrow I_{\rm E}$$

. 17

Output loop

$$(I_{\rm C} + I_{\rm B}) R_{\rm E} + R_{\rm C} I_{\rm C} - V_{\rm CC} + V_{\rm CE} = 0$$

Stability factor  $S = \frac{1+\beta}{1+\beta\left(\frac{R_{\rm E}}{R_{\rm E}+R_{\rm b}}\right)}$

$I_{\rm C}$  can be made insensitive to  $\beta$ , if we choose

$$R_{\rm E} >> R_{\rm b}$$

#### **Advantages**

- (i) Simplest biasing scheme

- (ii) Better stability over fixed Bias if  $R_{\rm E} >> \frac{R_{\rm B}}{(\beta + 1)}$

#### Disadvantages

(i) The resistor  $R_{\rm E}$  provides a negative feedback for AC input consequently reduces the gain

To increase the stability of the emitter feedback circuit, a bypass capacitor has been placed in parallel with  $R_{\rm F}$

The purpose of bypass capacitor is to make  $R_{\rm E} = 0$  for AC input and hence no gain reduction at the output of the circuit

#### **Collector-Emitter Feedback Bias**

By applying KVL to the circuit, the output loop will be as follows:

$$V_{\rm CC} - (I_{\rm C} + I_{\rm B}) R_{\rm C} - V_{\rm CE} - R_{\rm E} (I_{\rm C} + I_{\rm B}) = 0$$

Then, the input loop will be as follows:

$$V_{\rm CC} - (I_{\rm C} + I_{\rm B}) R_{\rm C} - I_{\rm B} R_{\rm b} - V_{\rm BE} - R_{\rm E} (I_{\rm B} + I_{\rm C}) = 0$$

Stability factor  $S = \frac{1 + \beta}{1 + \beta (R_{\rm e} + R_{\rm b})/(R_{\rm e} + R_{\rm c} + R_{\rm b})}$

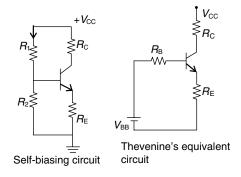

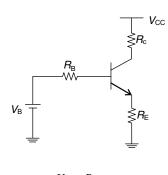

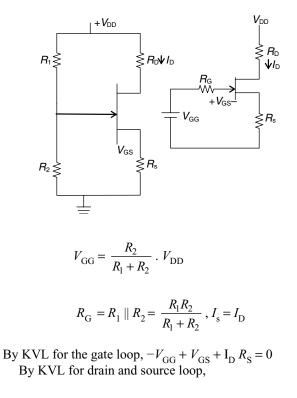

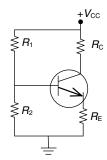

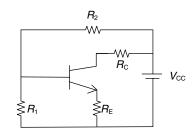

## Self-Bias, Emitter Bias, or Voltage-Divide Bias

$$V_{\rm BB} = \frac{R_2 \cdot V_{\rm CC}}{R_2 + R_1}, R_{\rm B} = \frac{R_2 R_1}{R_2 + R_1}$$

Input loop

$$V_{\rm BB} = I_{\rm B} R_{\rm B} + V_{\rm BE} + (I_{\rm b} + I_{\rm c}) R_{\rm e}$$

Output loop

$$V_{\rm cc} - R_{\rm C}I_{\rm c} + V_{\rm CE} + (I_{\rm b} + I_{\rm c})R_{\rm c}$$

Stability factor  $S = \frac{1+\beta}{1+\beta \left(\frac{R_{\rm E}}{R_{\rm E}+R_{\rm P}}\right)}$

KVL at input side is as follows:

$$V_{\rm BB} - I_{\rm B}R_{\rm B} - V_{\rm BE} - (I_{\rm B} + I_{\rm C})R_{\rm E} = 0$$

$$I_{\rm C} = \beta I_{\rm B}$$

$$\Rightarrow I_{\rm B} = \frac{V_{\rm BB} - V_{\rm BE}}{(\beta + 1)R_{\rm E} + R_{\rm B}} \Rightarrow I_{\rm C} = \frac{\beta(V_{\rm BB} - V_{\rm BE})}{(\beta + 1)R_{\rm E} + R_{\rm B}}$$

KVL at output side is as follows:

$$V_{\rm cc} - I_{\rm c} R_{\rm c} - V_{\rm CE} - (I_{\rm B} + I_{\rm c})R_{\rm E} = 0$$

$$\Rightarrow V_{\rm CE} = V_{\rm cc} - I_{\rm c} R_{\rm c} - (\beta + 1) I_{\rm B} R_{\rm E}$$

If ' $\beta$ ' is very large, then approximate value of

$$I_{\rm c} \simeq \frac{V_{\rm BE} - V_{\rm BE}}{R_{\rm E}}$$

Where

$$R_{\rm B} = R_1 || R_2$$

$V_{\rm BB} = \frac{V_{\rm CC} \cdot R_2}{R_1 + R_2}$

If  $(\beta + 1) R_{\rm E} >> R_{\rm B}$ , then  $I_{\rm c}$  is independent of ' $\beta$ '

1. Better stability over, all biasing schemes if

$$R_{\rm E} >> \frac{R_{\rm B}}{(1+\beta)}$$

2. Most of the amplifiers uses self-biasing scheme.

## **BIAS COMPENSATION**

#### Compensation Techniques

$$I_{\rm c} = f(I_{\rm co}, V_{\rm BE}, \beta)$$

$I_{co}$  (reverse saturation current),  $V_{BE}$ , and  $\beta$  are temperaturedependent parameters. Hence, to stabilize the circuit against the variation in temperature, that is, (to make  $I_c$  independent of  $I_{co}$ ,  $V_{BE}$ ,  $\beta$ ) compensation techinques are used.

- 1. Reverse saturation current doubles for every 10°C rise in temperature.

- 2.  $V_{\rm BE}$  decreases for 7.5 mv for 1°C rise in temperature

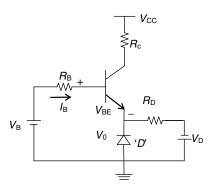

## Compensation for V<sub>BE</sub>

If the values of  $V_{\rm D}$  and  $R_{\rm D}$  are designed such that the voltage across the diode is  $V_{\rm BE}$  from P–N side,  $I_{\rm B}$  is  $V_{\rm B} - I_{\rm B}R_{\rm B} - V_{\rm BE}$ +  $V_{\rm BE} = 0$

$$I_{\rm B} = \frac{V_{\rm B}}{R_{\rm B}}$$

gives  $I_{\rm c} = \frac{\beta V_{\rm B}}{R_{\rm B}}$  independent of  $V_{\rm BE}$

$V_{\rm BE}$  tracks  $V_0$  with respect to temperature, and hence,  $I_{\rm C}$  will be insensitive to variations in  $V_{\rm BE}$ .

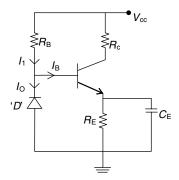

#### Compensation for I

Let us assume that the transistor and the diode are made up of same material. Hence,  $I_{co}$  is same for both

$$\therefore I_{\rm c} = \beta I_{\rm B} + (1 + \beta) I_{\rm co}$$

$I_{c} = \beta (I_{1} - I_{0}) + (1 + \beta) I_{co}$  (: from the Figure)

If ' $\beta$ ' is assumed to be so large and  $I_0 = I_{co}$

$$\Rightarrow \beta + 1 \simeq \beta$$

$$I_{c} = \beta I_{1} - \beta I_{0} + \beta I_{co}$$

$I_{\rm c} = \beta I_1$  which is independent of reverse saturation current.

If the diode and transistor are of the same type, and material, the reverse, saturation current of diode will increase with temperature at the same rate as the transistor collector saturation current  $I_{CO}$

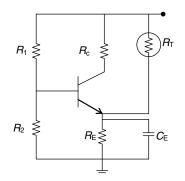

#### Thermistor Compensation

The thermistor has a negative temperature coefficient its resistance decreases exponentially with increase in temperature

As T rises,  $R_{\rm T}$  decreases, and the current fed through  $R_{\rm T}$  into  $R_{\rm e}$  increase. Since the voltage drop across  $R_{\rm e}$  is in the direction to reverse bias the transistor. The temperature sensitivity of  $R_{\rm T}$  acts so as to tend to compensate the increase in  $I_{\rm C}$ due to temperature.

#### Sensistor Compensation

Figure 1 R sensistor

Sensistor is having a positive temperature coefficient of resistance whose resistance increases, as temperature increases, (as the collector current is increasing). Hence, the current through sensistor decreases

$I_{\rm B} = I_1 - I_2$

$I_1$  decreases and  $I_{\rm B}$  also starts decreasing.

Since  $I_c = \beta I_B$  the collector current is in control, thus providing a better stability.

## THERMAL RUNWAY

Power dissipated at collector causes self-heating, as a consequence junction temperature rises, and in turn, this increases collector current with a subsequent increase in power dissipation. If this phenomenon (known as thermal runway) continues, it may result in permanently damaging the transistor.

### Thermal Resistance

It is found that steady-state temperature rises at the collector junction is proportional to the power dissipated at the junction.

$$\Delta T = T_{\rm J} - T_{\rm A} = \theta P_{\rm D}$$

$T_{\rm I}$  – Junction temperature  $T_{\rm A}$  –Ambient temperature  $P_{\rm D}$  – Power dissipated at collector junction  $\theta$  – Thermal resistance

The required condition for thermal stability is the rate at which heat is released must not exceed the rate at which the heat can be dissipated  $\frac{\partial P_{\rm C}}{\partial T_{\rm j}} < \frac{\partial P_{\rm D}}{\partial T_{\rm j}} \Rightarrow \frac{\partial P_{\rm C}}{\partial T_{\rm j}} < \frac{1}{\theta}$  is the condition to avoid thermal runwa

#### **Heat Sink**

It is a device that cools the diode or transistor by dissipating heat into surrounding.

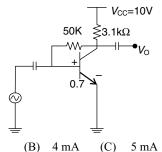

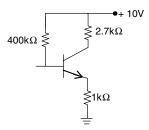

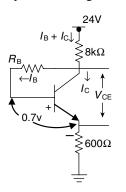

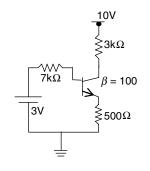

#### Example 2

Find the DC collector current if  $V_{\rm BF} = 0.7$  volts and ' $\beta$ ' is considered as very large

(A) 2 mA

Solution

(β

$$I_{\rm c} = \frac{\beta (V_{\rm CC} - V_{\rm BE})}{(\beta + 1)R_{\rm C} + R_{\rm B}}$$

(D) 3 mA

As ' $\beta$ ' is large

+ 1)

$$R_{\rm C} \simeq \beta R_{\rm C} >> R_{\rm B}$$

$I_{\rm C} \simeq \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm C}}$

$= \frac{10 - 0.7}{3.1 \mathrm{k}\Omega}$

$I_{\rm c} = 3 \mathrm{mA}.$

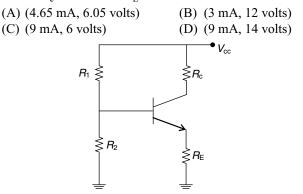

#### Example 3

A common emitter amplifier has a potential divider bias using  $V_{\rm cc} = 20$  volts,  $R_1 = R_2 = 6.2$  k $\Omega$  and  $V_{\rm BE} = 0.7$  volts,  $\beta$  is assumed to be so large then, the operating point is (Given  $R_c$  as 1 k $\Omega$  and  $R_E$  as 2 k $\Omega$ )

Solution

$$V_{\rm BB} = \frac{V_{\rm CC} \cdot R_2}{R_1 + R_2} = 10 \text{ volts}$$

$$R_{\rm B} = R_1 ||R_2 = 3.1 \text{ k}\Omega$$

$$I_{\rm c} = \frac{\beta(V_{\rm BB} - V_{\rm BE})}{(\beta + 1)R_{\rm E} + R_{\rm B}}$$

As ' $\beta$ ' is very large, that is,  $(\beta + 1) R_E >> R_B$

$$\therefore I_{c} \approx \frac{V_{BB} - V_{BE}}{R_{E}}$$

$$I_{c} = \frac{10 - 0.7}{3.1 \text{k}\Omega}$$

$$I_{c} = 4.65 \text{ mA}$$

Apply KVL at output side.

$$V_{\text{CEQ}} = V_{\text{cc}} - I_{\text{CQ}}R_{\text{c}} - I_{\text{E}}R_{\text{E}} \text{ as } `\beta' \text{ is large } I_{\text{E}} \simeq I_{\text{CQ}}$$

$$\therefore V_{\text{CEQ}} = V_{\text{cc}} - I_{\text{CQ}}(R_{\text{c}} + R_{\text{E}})$$

$$= 20 - (4.65 \text{ mA}) (1 + 2\text{k}\Omega)$$

$V_{\rm CEQ} = 6.05$  volts.

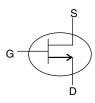

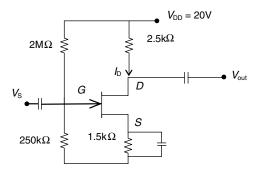

## BIASING THE FIELD EFFECT TRANSISTOR (FET)

1. Field Effect transistor (FET) is a voltage controlled Device having 3 terminals Gate, source and Drain

- 2. FET is a symmetrical Device (i.e. Source and Drain are interchangable)

- 3. FET acts as a better switch over BJT

For junction field effect transistor (JFET) and depletion mode MOSFET'S Shockley's equation is valid.

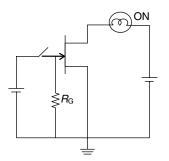

$R_{\rm G}$  is called the bleeder Resistor, FET is ON when input circuit is open

$$\therefore I_{\rm G} = 0$$

Transfer characteristics

Transfer characteristics are governed by the equation

$$I_{\rm D} = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right)^2$$

When  $I_{\rm D}$  = drain current,  $I_{\rm D} = I_{\rm DSS}$ . When  $V_{\rm GS}$  = 0, that is, drain saturation current  $V_{\rm P}$  = pinch off voltage.

#### 3.472 | Part III • Unit 5 • Analog Circuits

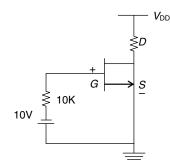

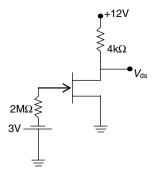

#### Example 4

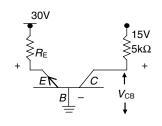

Find  $I_D$ ,  $V_{GS}$  for the given circuit assuming  $V_{DD} = 30$  volts,  $V_P = -5$  volts,  $I_{DSS} = 30$  mA

(A) 0.27 amp, 10 volts

(B) 0.27 amp, 20 volts

(C) 0.135 amp, 10 volts

(D) 0.27 amp, -10 volts

#### Solution

$$I_{\rm G} = 0$$

Amps

Apply KVL at input side gives

$$-10 - V_{GS} - 0 (10k) = 0$$

$$V_{GS} = -10 \text{ volts}$$

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2}$$

$$= 30 \text{ mA} \left[ 1 + \frac{10}{5} \right]^{2}$$

$$= 270 \text{ mA}$$

$$I_{D} = 0.27 \text{ amps.}$$

In MOS circuits biasing schemes, control deviations in the operating point caused by fabrication variations in the threshold voltage  $V_{\rm T}$  and transconductance (processing) parameter k. Both integrated circuits and discrete component JFET circuits are biased so that the effects of unit to unit variations in the pinch off voltage  $V_{\rm p}$  and zero bias drain saturation current  $I_{\rm DSS}$  are controlled.

| BJT                                       | FET                                                                                            |

|-------------------------------------------|------------------------------------------------------------------------------------------------|

| (i) Current-controlled device.            | (i) Voltage-controlled device.                                                                 |

| (ii) Apply KVL at input gives $I_{\rm B}$ | (ii) $I_{\rm G} = 0$ Amps                                                                      |

| (iii) $I_{\rm C} = \beta I_{\rm B}$       | (iii) $I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right]^2$              |

| (iv) Not symmetrical                      | <ul> <li>(iv) Symmetrical device</li> <li>(source and drain are<br/>interchangable)</li> </ul> |

#### **Four-Resistor Bias Circuit**

$$-V_{\rm DD} + R_{\rm D} I_{\rm D} + V_{\rm DS} + R_{\rm S} I_{\rm D} = 0$$

In this analysis,  $I_{\rm G} = 0$  was assumed. However, the small reverse saturation current  $I_{\rm GSS}$  exits in the gate loop. The resistance  $R_{\rm G}$  is selected to be as large as it is feasible while maintaining the voltage drop ( $I_{\rm GSS} R_{\rm G} << V_{\rm GG}$ ) at a negligible value.

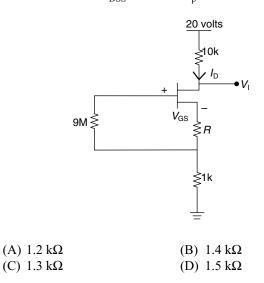

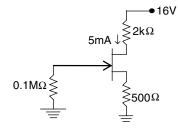

#### Example 5

Find the value of resistor '*R*'. If the drain to ground voltage = 0. Given  $I_{\text{DSS}} = 50$  mA,  $V_{\text{p}} = -6$  volts

Solution

$$I_{\rm G} = 0 \text{ Amps}$$

$$I_{\rm D} = \frac{20 - V_{\rm D}}{10 \text{k}}$$

$$I_{\rm D} = \frac{20 - 0}{10 \text{k}} \simeq 2 \text{ mA}$$

$$I_{\rm D} = I_{\rm S} = 2 \text{ mA}$$

$$I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right]^2$$

$$2 \text{ mA} = 50 \text{ mA} \left[ 1 + \frac{V_{\rm GS}}{6} \right]^2$$

$$\Rightarrow 1 + \frac{V_{\rm GS}}{6} = \frac{1}{5}$$

$$\Rightarrow V_{\rm GS} = -4.8 \text{ volts}$$

KVL at input gives

$$-V_{GS} - I_D[R + 1 \text{ k} \Omega] = 0$$

$$\Rightarrow 4.8 = I_D[R + 1 \text{ k}\Omega]$$

$$\Rightarrow 4.8 = 2 \text{ mA} [R + 1 \text{ k}\Omega]$$

$$\Rightarrow R = 1.4 \text{ k}\Omega.$$

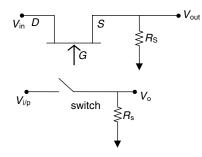

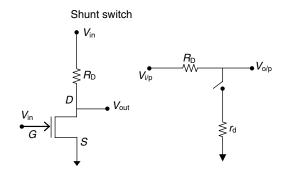

## **JFET as Analog Switch**

$\Rightarrow$

JFET can be used as multiplexer, amplifier, switch, etc. Major application of JFET is analog switch.

For analog switch, we consider two points that are lie in cut-off and saturation region.

If FET is in saturation region, then it acts as a closed switch. If it is in cut-off region, then it acts as an open switch.

FET can be used as a series switch or shunt switch

#### **Series Switch**

FET as a series switch, equivalent circuit.

### **Shunt Switch**

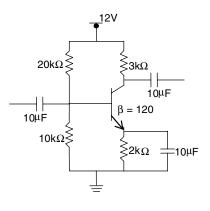

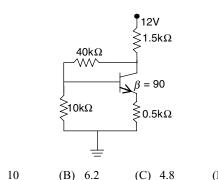

#### **Example 6**

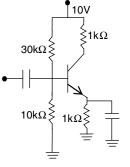

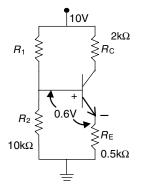

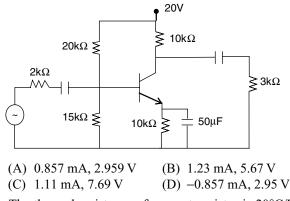

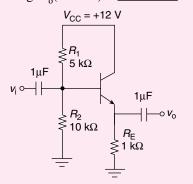

A common emitter amplifier has a potential divider bias using  $V_{\rm CC} = 12$ V. If  $R_{\rm C} = 4$  k $\Omega$ ,  $R_{\rm E} = 1$  k $\Omega$ ,  $R_{\rm 1} = 20$  k $\Omega$ ,  $R_{\rm 2} = 5$  k $\Omega$ ,  $V_{\rm BE} = 0.6$  V,  $\beta = 100$ , and then, the operating point is

(A) 5 V, 1 mA (C) 5.14 V, 1.2 mA

(B) 4 V, 1.4 mA (D) 3.41 V, 1.71 mA

Solution

$$V_{\rm B} = \frac{R_2}{R_1 + R_2} \times V_{\rm CC} = \frac{5}{20 + 5} \times 12 = 2.4 \text{V}$$

Writing KVL for the base-emitter loop

$$V_{\rm B} = I_{\rm B} \cdot R_{\rm B} + V_{\rm BE} + (I_B + I_{\rm C})R_{\rm E}$$

$$R_{\rm B} = \frac{R_1 \cdot R_2}{R_1 + R_2} = \frac{20 \times 5}{20 + 5} = 4k\Omega, \ I_{\rm B} = \frac{I_{\rm C}}{\beta}$$

$$2.4 = \frac{I_{\rm C}}{100} \times 4 + 0.6 + \left(\frac{I_{\rm C}}{100} + I_{\rm C}\right) \times 1$$

$$1.8 = \frac{21}{20} \cdot I_{\rm C} \Rightarrow I_{\rm C} = 1.714 \,\mathrm{mA}$$

Writing KVL for the collector loop

$$V_{\rm CC} = I_{\rm C} \cdot R_{\rm C} + V_{\rm CE} + (I_{\rm C} + I_{\rm B})R_{\rm E}$$

$$12 = 1.714 \times 4 + V_{\rm CE} + \left(1.714 + \frac{1.714}{100}\right) \times 1$$

$$V_{\rm CE} = 3.41 \text{V}$$

#### Example 7

When  $\beta$  is doubled, what are the operating point and stability factor in the previous problem?

(A) 1.756 mA, 3.21 V, 4.9

- (B) 1.71 mA, 3.14 V, 4.9

- (C) 1.71 mA, 3.21 V, 4.81

- (D) 1.756 mA, 3.21 V, 4.81

#### Solution

$$V_{\rm B} = 2.4 \text{V}, R_{\rm B} = 4 \text{k}\Omega, I_{\rm B} = \frac{I_{\rm C}}{\beta} = \frac{I_{\rm C}}{200}$$

Writing KVL for the base-emitter loop

$$V_{\rm B} = I_{\rm B} \cdot R_{\rm B} + V_{\rm BE} + (I_{\rm B} + I_{\rm C})R_{\rm E}$$

$$2.4 = \frac{I_{\rm C}}{200} \times 4 + 0.6 + \left(\frac{I_{\rm C}}{200} + I_{\rm C}\right) \times 1$$

$$= \frac{5}{200} I_{\rm C} + I_{\rm C} + 0.6$$

$$1.8 = 1.025I_{\rm C} \Rightarrow I_{\rm C} = 1.756 \text{ mA}$$

Writing KVL for the collector loop

$$V_{\rm CC} = I_{\rm C} \cdot R_{\rm C} + V_{\rm CE} + (I_{\rm C} + I_{\rm B})R_{\rm E}$$

12 = 1.756 × 4 +  $V_{\rm CE} + \left(\frac{1.756}{200} + I_{\rm C}\right) \times 1$

$V_{\rm CE} = 3.21 \text{ V}$

$$S_{1} = (\beta + 1) \frac{1}{1 + \frac{\beta R_{\rm E}}{R_{\rm B} + R_{\rm E}}} = \frac{201}{1 + \frac{200}{4 + 1}} = 4.9024$$

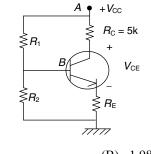

#### Example 8

A silicon transistor with  $\beta = 100$  is to be used in the selfbiasing circuit, shown in figure such that the quiescent point corresponds to  $V_{\rm CE}$  = 10 V and  $I_{\rm C}$  = 2 mA, find ' $R_{\rm E}$ ' if  $V_{\rm CC}$  = 24 V,  $R_{\rm C} = 5 \,\mathrm{k}\Omega?$

(A)

$$2 k\Omega$$

(B)  $1.98 k\Omega$

(C)  $980\Omega$  (D)  $R_1 || R_2$

#### Solution

(

By applying KVL between  $V_{\rm CC}$  and ground,

$$V_{\rm CC} = V_{\rm RC} + V_{\rm CE} + V_{\rm RE}$$

=  $I_{\rm C}R_{\rm c} + V_{\rm CE} + (I_{\rm B} + I_{\rm c})R_{\rm E}$

24V =  $2 \times 10^{-3} \times 5 \times 10^{3} + 10 + \left(\frac{2 \times 10^{-3}}{100} + 2 \times 10^{-3}\right) \cdot R_{\rm E}$

$\Rightarrow R_{\rm E} = \frac{4}{2 \times 10^{-3}(1.01)} = 1.98 \,\mathrm{k\Omega}$

#### **Example 9**

In the above question, it is desired to have  $S \leq 3$ , find the limiting value of  $R_1$  and  $R_2$  assuming  $V_{\text{BE (active)}} = 0.65$  V. (A) 41.39 kΩ, 10.16 kΩ (B) 20.69 kΩ, 10.16 kΩ (C) 20.69 k $\Omega$ , 5.08 k $\Omega$ (D) 41.39 kΩ, 5.08 kΩ

#### Solution

$$S = \frac{(\beta + 1)(R_{\rm B} + R_{\rm E})}{R_{\rm B} + R_{\rm E}(\beta + 1)} = \frac{R_{\rm B} + R_{\rm E}}{R_{\rm E} + \frac{R_{\rm B}}{\beta + 1}}$$

$$3 = \frac{101(R_{\rm B} + 1.98)}{R_{\rm B} + 1.98(101)}$$

$3R_{\rm B} + 599.94 = 101R_{\rm B} + 199.98$

$$98R_{\rm B} = 3999.96 \Longrightarrow R_{\rm B} = 4.08 \mathrm{k}\Omega$$

$$R_{\rm B} < 4.08 \mathrm{k}\Omega$$

for  $S \leq 3$

$$R_{\rm B} = \frac{R_{\rm I}R_{\rm 2}}{R_{\rm I} + R_{\rm 2}}, V_{\rm B} = V_{\rm CC} \cdot \frac{R_{\rm 2}}{R_{\rm I} + R_{\rm 2}}$$

By solving

$$R_{1} = \frac{V_{CC} \cdot R_{B}}{V_{B}}, R_{2} = \frac{R_{I}V_{B}}{V_{CC} - V_{B}}$$

$$V_{B} = I_{B} \cdot R_{B} + V_{BE} + V_{RE}$$

$$= 0.02 \times 10^{-3} \times 4.08 \times 10^{3} + 0.65 + 4$$

$$= 4.7312 \text{ V}$$

$$R_{1} = \frac{24 \times 4.08}{4.7312} = 20.69 \text{k}\Omega$$

$$R_{2} = \frac{20.69 \times 4.7312}{24 - 4.73} = 5.08 \text{k}\Omega$$

#### Example 10

Consider the transistor circuit of figure where  $V_{cc} = 24$  V,  $R_{C} = 5.6$  k $\Omega$ ,  $R_{E} = 1$  k $\Omega$ ,  $R_{2} = 10$  k $\Omega$ , and  $R_{1} = 80$  k $\Omega$ ,  $\beta = 60$ ,  $V_{BE} = 0.6$  V, the transistor operates in the active region. The operating point of the transistor is

| (A) 1.78 mA, 13.254 V | (B) 1.78 mA, 12.28 V |

|-----------------------|----------------------|

| (C) 1.39 mA, 13.25 V  | (D) 1.39 mA, 12.28 V |

#### Solution

$$R_{\rm B} = \frac{R_1 R_2}{R_1 + R_2} = \frac{80x10}{80 + 10} = 8.89 \text{k}\Omega$$

The operating point can be found from the forward characteristics by writing the bias equation

$$I_{\rm B} = \frac{I_{\rm C}}{\beta} = \frac{I_{\rm C}}{60}$$

$$V_{\rm B} = I_{\rm B}R_{\rm B} + V_{\rm BE} + I_{\rm E}R_{\rm E}$$

$$\frac{V_{\rm CC} \cdot R_2}{R_1 + R_2} = I_{\rm B}R_{\rm B} + V_{\rm BE} + (I_{\rm C} + I_{\rm B})R_{\rm E}$$

$$\frac{24 \times 10}{80 + 10} = I_{\rm B} \times 8.89 + 0.6 + (60 + 1)I_{\rm B} \times 1$$

$$2.67 = I_{\rm B}(69.89) + 0.6$$

$$I_{\rm B} = 0.0296 \text{mA} \Rightarrow 29.6 \mu \text{A}$$

$$I_{\rm C} = 60 \times 29.6 \mu \text{A} = 1.78 \text{mA}$$

$$V_{\rm CE} = V_{\rm CC} - I_{\rm C}R_{\rm C} - (I_{\rm B} + I_{\rm C}) \cdot R_{\rm E} = 12.23 \text{V}$$

$$(I_{\rm CQ}, V_{\rm CEQ}) = (1.78 \text{mA}, 12.23 \text{V})$$

#### Example 11

The stability factor of the above transistor is(A) 1.99(B) 3.13(C) 6.31(D) 8.63

#### Solution

$$S = \frac{R_{\rm B} + R_{\rm E}}{R_{\rm E} + \frac{R_{\rm B}}{\beta + 1}} = \frac{8.89 + 1}{1 + \frac{8.89}{61}} = 8.63$$

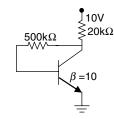

#### Example 12

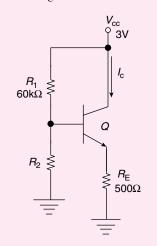

The fixed bias circuit as shown is used as collector bias circuit, the value of  $R_{\rm B}$  is? Quiescent point (9.2 mA, 4.4 V), the transistor has DC current gain 115.  $V_{\rm BE} = 0.7$  V,  $V_{\rm CC} = 9$  V,  $R_{\rm C} = 500 \Omega$ .

## (A) 500 Ω(C) 75.42 kΩ

## (B) 45.75 kΩ (D) 125.63 kΩ

Solution

$$V_{\rm CC} = (I_{\rm B} + I_{\rm C})R_{\rm C} + I_{\rm B} \cdot R_{\rm B} + V_{\rm BE}$$

$$9 = \left(\frac{9.2}{115} + 9.2\right) \times 0.5 + \frac{9.2}{115} \times R_{\rm B} + 0.7$$

$$R_{\rm B} = \frac{3.66}{0.08} = 45.75 \text{k}\Omega$$

#### Example 13

The stability factor and the thermal stability factor for the above circuit are

(A) 62.81 and 0.525

(B) 51.71 and 0.446

(C) 42.36 and 0.345

(D) 33.81 and 0.824

#### Solution

$$S = \frac{1 + h_{\rm FE}}{1 + \frac{h_{\rm FE} \cdot R_{\rm C}}{R_{\rm C} + R_{\rm B}}} = \frac{1 + 115}{1 + \frac{115 \times 0.500}{0.5 + 45.75}} = 51.711$$

Thermal stability factor  $K = \frac{S}{1 + h_{\text{FE}}} = \frac{51.7111}{116} = 0.446$

#### Example 14

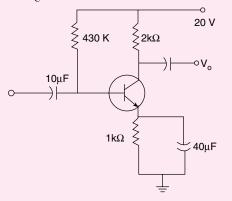

FET voltage divider bias is shown in given figure. If  $I_{\rm D} = 4$  mA, then  $V_{\rm GS}$  and  $V_{\rm DS}$  will be respectively

#### 3.476 | Part III • Unit 5 • Analog Circuits

(A) -3.78 V, 4 V (C) -3.78 V and -4 V

#### Solution

$$V_{\rm G} = \frac{20 \times 0.25}{2 + 0.25} = \frac{20}{9}$$

#### Exercises

#### **Practice Problems I**

Direction for questions 1 to 25: Select the correct alternative from the given choices.

(B) 4 V and -3.78 V

(D) -4 V and -3.78 V

1. For the circuit showing in figure assume  $\beta = 100$  for BJT, the transistor will be in

- (A) Cut-off region (B) Active region

- (C) Inverse active region (D) Saturation region.

- 2. For the given biasing network, the stability factor 'S' is

(A) 101 (B) 17.14 (C) 20.84 (D) 34

3. In a fixed bias circuit, S = 51 for  $I_c = 2$  mA. Given  $V_{cc} =$ 10volt. The value of  $R_{\rm B}$  is

(A) 250 kΩ (B) 250 Ω (C)  $25 \text{ k}\Omega$ (D)  $2.5 \text{ k}\Omega$

4. In the given fixed bias circuit,  $V_{CE(sat)} = 0$  volt, the minimum value of  $I_{\rm B}$  to saturate the transistor is \_

- (C) 0.133 mA

- 5. For the given biasing network,  $\beta$  is taken as very large. Assume  $V_{\rm BE} = 0.2$  V, the value of  $I_{\rm E}$  and  $V_{\rm CE}$  are \_\_\_\_\_

(D) 0.16 mA

$$V_{GS} = V_G - I_D \cdot R_S = \frac{20}{9} - 4 \times 1.5 = -3.78V$$

$$V_{DS} = V_{DD} - I_D (R_S + R_D)$$

$$= 20 - 4 \times (1.5 + 2.5) = 4V$$

- (B) '0'mA, 10 V (A) 2.3 mA, 0 V (C) 10 mA, 5.4 V (D) 2.3 mA, 5.4 V

- 6. A Ge transistor is used in the self-bias arrangement with  $V_{\rm CC} = 20$  V,  $R_{\rm C} = 2$  k $\Omega$ ,  $R_{\rm E} = 500$   $\Omega$ . The Q-point is selected at  $V_{\rm CE} = 10$  V,  $I_{\rm C} = 5$  mA and S = 12. If  $V_{\rm BE}$ = 0.3 V and  $\beta$  = 60, then the values of  $R_1$  and  $R_2$  are

| (A) | 40.65 kΩ, 8.24 kΩ | (B) 8.24 kΩ, 40.65 kΩ                 |

|-----|-------------------|---------------------------------------|

| (C) | 40.65 kΩ, 18.6 kΩ | (D) 18.6 k $\Omega$ , 4.65 k $\Omega$ |

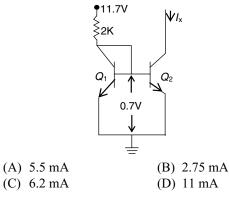

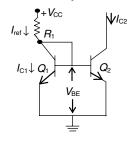

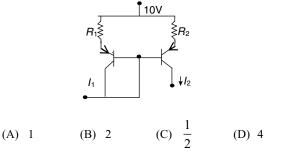

7. In the BJT current mirror shown below, assume that the emitter area of  $Q_1$  is double that of  $Q_2$ . What is the value of  $I_{\rm v}$ ?

8. The transistor has following parameters.  $\beta = 50$  and  $V_{\rm BE} =$ 0.6 V. If  $\beta$  is increased by 5%, what is the change in  $V_{\rm CE}$ ?

- (A) increased by 4.57% (B) increased by 2.97%

- (C) decreased by 4.57% (D) decreased by 2.97%

- 9. A Si transistor with  $\beta = 50$  at 50°c is used, and it is desired that  $V_{\rm CE} = 8$  V. Consider  $I_{\rm CO}$  varies from 0.5 to 10  $\mu$ A when temperature changes from 50°c to 100°c.

The values of  $R_{\rm B}$ , stability factor, and  $I_{\rm c}$  at 100°c are, respectively \_\_\_\_\_

- (A)  $200 \text{ k}\Omega$ , 51, 2.5 mA

- (B)  $20.5 \text{ k}\Omega, 50, 1 \text{ mA}$

- (C) 200.5 k $\Omega$ , 16.7, 1.98 mA

- (D)  $2 k\Omega$ , 10.4, 1.75 mA

- **10.** Given  $I_{\text{DSS}} = 6$  mA and  $V_{\text{P}} = -4$  V for the given FET biasing Network, the value of  $V_{\text{DS}}$  is \_\_\_\_\_

11. A self-bias network with FET is given below; it has  $I_{\rm D} = 5 \text{ mA}$

What are the values of  $V_{GS}$  and  $V_{DS}$ ?

(A) -2.5 V, -2.5 (C) -5 V, 0 V (D) 0 V, -5 V 12. For the given biasing network, calculate  $I_{\rm B}$  and  $V_{\rm CE}$  (assume  $V_{\rm BE}$  = 0.7 V)

- (A) 13.4μA, 3.95V

(B) 13.4μA, 6V

(C) 1.34μA, 3.95V

(D) 1.34μA, 6V

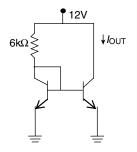

- 13. A constant current source using two matched N-P-N transistors with  $\beta = 100$  and  $V_{BE} = 0.6$  V is shown. Calculate  $I_{out}$

- (A) 1.5 mA (C) 1.86 mA (D) 2 mA

- 14. A transistor with  $V_{\rm BE} = 0.7$  V is shown. The values of  $R_1$  and  $R_2$  are such that the transistor is operating at  $V_{\rm CE} = 5$  V and  $I_{\rm C} = 2$  mA where  $\beta = 100$ . What is the operating point values for a transistor with  $\beta = 200$ .

- (A) 3.78 V, 3.1 mA

(B) 3.5 V, 2.6 mA

(C) 5 V, 2.5 mA

(D) 3.5 V, 1.25 mA

- 15. A transistor with  $\beta = 100$  is used in CE mode. It is connected in collector to base bias mode with  $\frac{R_{\rm B}}{R_{\rm C}} = 9$ . Calculate the stability factor? (A) 99 (B) 19.1 (C) 20.86 (D) 9.18

- **16.** Calculate the stability factor for the given biasing network.

17. For a given FET-biasing network,  $V_{\rm DS} = \frac{1}{2} V_{\rm DD}$ , what are the values of  $I_{\rm D}$  and  $V_{\rm GS}$ ?

| (A) | 1 mA, -1 V   | (B) | 10 mA, -1 V   |

|-----|--------------|-----|---------------|

| (C) | 1 mA, -1.5 V | (D) | 10 mA, -1.5 V |

**18.** The values of resistors  $R_{\rm C}$ ,  $R_{\rm E}$ , respectively, for  $I_{\rm C} = 5$  mA,  $V_{\rm CE} = 8$  V,  $V_{\rm E} = 6$  V, and  $S(I_{\rm co}) = 10$ ,  $h_{\rm fe} = 200$ , and  $V_{\rm CC} = 20$  V, are?

| (A) | 1.194 kW, 1.2 kΩ          | (B) 1.2 kW, 1.194 kΩ        |

|-----|---------------------------|-----------------------------|

| (C) | 10.3 kW, 17.43 k $\Omega$ | (D) 2.1 kW, 4.12 k $\Omega$ |

19. The values of resistors R<sub>1</sub> and R<sub>2</sub> in the above circuit are

(A) 17.2 kW, 32.86 kΩ

(B) 12.8 kW, 23.6 kΩ

(C) 12.8 kW, 22.86 kΩ

(D) 17.2 kW, 32.86 kΩ

#### Practice Problems 2

*Direction for questions 1 to 18:* Select the correct alternative from the given choices.

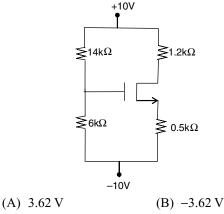

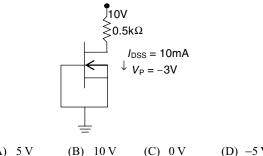

1. For the given biasing network, the collector to emitter voltage  $V_{CE}$  is \_\_\_\_\_ volt.

- **20.** A P-N-P transistor uses potential divider bias  $V_{BE} = -0.7 \text{ V}$ , and  $\beta = 100$ , the operating point is to be at  $I_C = -1 \text{ mA}$ , and  $V_{CE} = -5 \text{ V}$ ,  $V_{CC} = -20 \text{ V}$ , voltage drop across  $R_E \text{ is } -3 \text{ V}$ , for SC( $I_{co}$ ) = 5, the value of  $R_C$  and  $R_E$  are (A) 12 k $\Omega$ , 3 k $\Omega$  (B) 11.7 k $\Omega$ , 2.97 k $\Omega$  (C) 11.7 k $\Omega$ , 3 k $\Omega$  (D) 12 k $\Omega$ , 2.97 k $\Omega$

- 21. The values of R<sub>1</sub> and R<sub>2</sub> (bias resistances) in the above problem are?

(A) 4.2 kΩ, 12.4 kΩ

(B) 64.4 kΩ, 15.35 kΩ

- (C)  $42 k\Omega$ ,  $12 k\Omega$  (D)  $6.3 k\Omega$ ,  $24 k\Omega$

#### Direction for questions 22 to 24:

22. In the current circuit, if the transistor parameters are  $V_{\rm th}$

= 2 V,  $k_{\rm n} = 60\mu$ A/v<sup>2</sup>,  $\frac{W}{L} = 60$ , and the transistor is in saturation, the value of  $V_{\rm GS}$  is

(C)

$$0.74 \text{ V}$$

(D)  $-0.74 \text{ V}$

- **23.** The value of  $I_D$  is

(A) 12.5 mA

(B) 9.2 mA

(C) 6.3 mA

(D) 4.7 mA

- **24.** The value of  $V_{\text{DS}}$  is (A) 12.95 V (B) 11.9 V (C) 9.3 V (D) 7.5 V

- **25.** A BJT for which the manufacturer specifies  $P_{D(max)} = 125$  mw at 25°c free air temperature and max junction temperature is 150°c. The thermal resistance of BJT is

| (A) $5^{\circ}c/w$ | (B) $1^{\circ}c/mw$ |

|--------------------|---------------------|

| (C) 1°c/w          | (D) 10°C/mW         |

2. A current mirror shown below, provide a 1.5mA current with  $V_{\rm CC} = 12$  V. Assume  $\beta = 150$  and  $V_{\rm BE} = 0.7$  volts. What is  $R_1$ ?

| (A) 9.25 kΩ | (B) 7.43 kΩ |

|-------------|-------------|

| (C) 7.53 kΩ | (D) 8.5 kΩ  |

3. In the figure given,  $I_1 = 10 \ \mu\text{A}$  and  $I_2 = 40 \ \mu\text{A}$ . What is the ratio  $R_1/R_2$ .

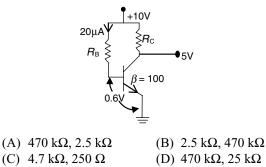

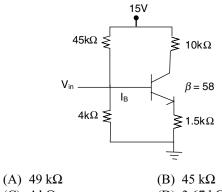

4. In the given biasing network, the value of  $R_{\rm B}$  and  $R_{\rm C}$  are \_\_\_\_\_

5. A transistor with emitter to base bias is given below.

The values  $\beta$  of transistor, the base resistance  $R_{\rm B}$  are

| (A) 100, 155 kΩ  | (B) 166, 1.75 MΩ |

|------------------|------------------|

| (C) 333, 1.55 MΩ | (D) 158, 1.8 MΩ  |

6. The self-bias network is given below. Its stability factor (S) is\_\_\_\_\_

- (A) 101 (B) 9.5 (C) 58 (D) 2

- 7. The value of  $R_{\rm E}$  which will saturate the transistor is nearly \_\_\_\_\_ k\Omega.

(A) 5 (B) 25 (C) 10 (D) 20 8. Calculate  $I_{\rm D}$  and  $V_{\rm GS}$  for  $V_{\rm DS} = 2$  V

- (A) 4.6 mA, -1.85 V (B) 3.8 mA, -0.63 V (C) 4.6 mA, -0.63 V (D) 3.8 mA, -1.85 V

- 9. Find the region of operation of transistor.

| (A) saturation | (B) active |

|----------------|------------|

| (C) cut-off    | (D) none   |

#### 3.480 Part III • Unit 5 • Analog Circuits

10. A FET-biasing network is used with following | 14. The equivalent base resistance of the given circuit is specifications.

$V_{\rm P} = 5 \text{ V}, I_{\rm DSS} = 8 \text{ mA}$ Calculate  $g_m$ ?

(A) 1.6 mS (B) 2 mS (C) 10 mS (D) 2.3 mS

11. The figure below shows a MOSFET-biasing network. Calculate  $V_{\rm DS}$ .

- (A) 5 V (C) 0 V (D) -5 V

- 12. A transistor with  $\beta$  is assumed to be very large is shown below. What is the value of  $R_1$  required to make  $I_{\rm C} = 2.5 \, {\rm mA}.$

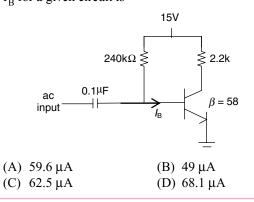

(A)  $2 k\Omega$ (B) 10k Ω (C) 44 kΩ (D) 54 kΩ **13.**  $I_{\rm B}$  for a given circuit is

- (C) 4 kΩ (D) 3.67 kΩ

- 15. The circuit shown in figure is that of a fixed bias circuit. Estimate the values of the collector load resistor  $R_c$ , and bias resistor  $R_{\rm B}$ , If the quiescent collector current and voltage values are 10 mA and 5 V, respectively. The transistor has a dc current gain of 110.  $V_{\text{BE}}$  is 0.7 V,  $V_{\text{CC}} = 12$  V.

| (A) | 500 Ω, 103.7 kΩ | (B) 500 Ω, 124.3 kΩ |

|-----|-----------------|---------------------|

| (C) | 700 Ω, 124.3 kΩ | (D) 700 Ω, 103.7 kΩ |

16. Calculate the thermal stability factor for the above circuit?

(A) 111 (B) 1 (C) 12 (D) 18

17. The circuit gives details for one stage of a transistor amplifier. Calculate the quiescent values of  $I_{\rm E}$ ,  $V_{\rm CE}$ ,  $h_{\rm fe} = 100, V_{\rm BE} = 0.$

**18.** The thermal resistance of power transistor is  $20^{\circ}$ C/W. The ambient temperature is 40°C and junction temperature is 160 . If  $V_{CE} = 4.2$  V, the maximum the collector can carry without destruction is (C) 1.66 A (A) 1.2 A (B) 2.5 A (D) 2 A

#### **PREVIOUS YEARS' QUESTIONS**

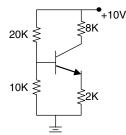

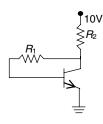

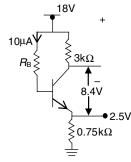

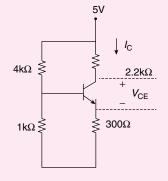

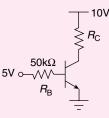

1. Assuming that the b of the transistor is extremely large and  $V_{\rm BE} = 0.7$  V,  $I_{\rm C}$ , and  $V_{\rm CE}$  in the circuit shown in figure, are [2004]

- (A)  $I_{\rm C} = 1 \text{ mA}, V_{\rm CE} = 4.7 \text{ V}$

- (B)  $I_{\rm C} = 0.5 \text{ mA}, V_{\rm CE} = 3.75 \text{ V}$

- (C)  $I_{\rm C} = 1 \text{ mA}, V_{\rm CE} = 2.5 \text{ V}$

- (D)  $I_{\rm C} = 0.5 \text{ mA}, V_{\rm CE} = 3.9 \text{ V}$

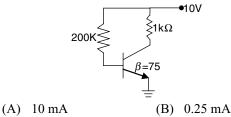

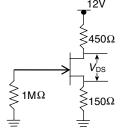

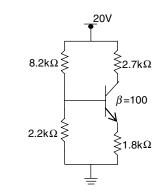

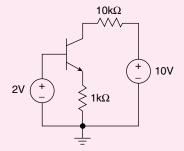

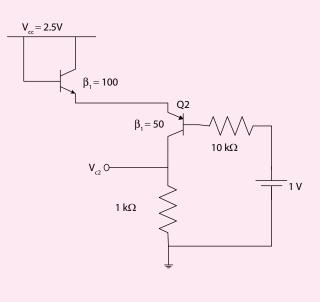

- 2. The circuit using a BJT with  $\beta = 50$  and  $V_{BE} = 0.7$  V is shown in figure. The base current  $I_B$  and collector voltage  $V_C$  are respectively. [2005]

(A) 43 μA and 11.4 volts(C) 45 μA and 11 volts

(B) 40 µA and 16 volts(D) 50 µA and 10 volts

Direction for questions 3 to 5:

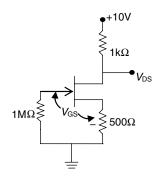

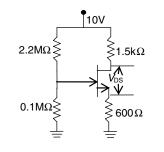

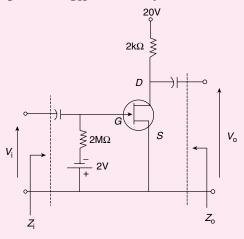

Given  $r_{d} = 20 \text{ k}\Omega$ ,  $I_{DSS} = 10 \text{ mA}$ ,  $V_{P} = -8 \text{ V}$ .

- **3.**  $Z_i$  and  $Z_0$  of the circuit are respectively. [2005]

- (A) 2 M $\Omega$  and 2 k $\Omega$  (B) 2 M $\Omega$  and  $\frac{20}{11}$  k $\Omega$

- (C) Infinity and  $2 k\Omega$  (D) Infinity and  $\frac{20}{11} k\Omega$

- 4.  $I_{\rm D}$  and  $V_{\rm DS}$  under DC conditions are respectively. [2005]

- (A)  $\,$  5.625 mA and 8.75 V

- (B) 7.500 mA and 5.00 V

- (C) 4.500 mA and 11.00 V

- (D) 6.250 mA and 7.50 V

- 5. Transconductance in millisiemens (mS) and voltage gain of the amplifier are respectively. [2005]

- (A) 1.875 mS and 3.41

- (B) 1.875 mS and -3.41

- (C) 3.3 mS and -6

- (D) 3.3 mS and 6

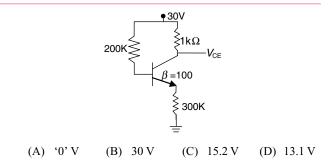

- 6. For the BJT circuit shown, assume that the  $\beta$  of the transistor is very large and  $V_{\rm BE} = 0.7$  V. the mode of operation of the BJT is: [2007]

- (A) cut-off (B) saturation

- (C) normal active (D) reverse active

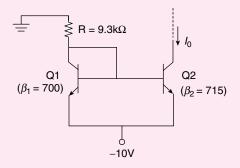

- 7. In the silicon BJT circuit shown below, assume that the emitter area of transistor  $Q_1$  is half that of transistor  $Q_2$ . [2010]

The value of current  $I_0$  is approximately (A) 0.5 mA (B) 2 A (C) 9.3 mA (D) 15 mA

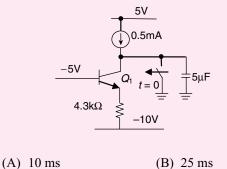

8. For the BJT,  $Q_1$  in the circuit shown as follows,  $\beta = \infty$ ,  $V_{\text{BEon}} = 0.7$  V,  $V_{\text{CEsat}} = 0.7$  V. The switch is initially closed. At time t = 0, the switch is opened. The time t at which  $Q_1$  leaves the active region is [2011]

- (C) 50 ms (D) 100 ms

- **9.** For a BJT, the common-base current gain  $\alpha = 0.98$  and the collector base junction reverse bias saturation current  $I_{\rm CO} = 0.6 \,\mu\text{A}$ . This BJT is connected in the common emitter mode and operated in the active region with a base drive current  $I_B = 20 \,\mu\text{A}$ . The collector current  $I_C$  for this mode of operation is

|             |             | [2011] |

|-------------|-------------|--------|

| (A) 0.98 mA | (B) 0.99 mA |        |

| (C) 1.0 mA  | (D) 1.01 mA |        |

**10.** In the circuit shown below, the silicon npn transistor Q has a very high value of  $\beta$ . The required value of  $R_2$  in k $\Omega$  to produce  $I_C = 1$  mA is [2013]

(A) 20 (B) 30 (C) 40 (D) 50

[2014]

11. A good current buffer has

- (A) low-input impedance and low-output impedance

- (B) low-input impedance and high-output impedance

- (C) high-input impedance and low-output impedance

- (D) high-input impedance and high-output impedance

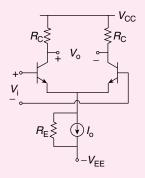

12. In the differential amplifier shown in the figure, the magnitudes of the common-mode and differential-mode gains are  $A_{cm}$  and  $A_d$ , respectively. If the resistance  $R_E$  is increased, then [2014]

- (A)  $A_{\rm cm}$  increases

- (B) common-mode rejection ratio increases

- (C)  $A_{d}$  increases

- (D) common-mode rejection ratio decreases

- **13.** In the circuit shown, the silicon BJT has  $\beta = 50$ . Assume  $V_{\text{BE}} = 0.7$  V and  $V_{\text{CE(sat)}} = 0.2$  V. Which one of the following statements is correct? **[2014]**

- (A) For  $R_{\rm C} = 1 \text{ k}\Omega$ , the BJT operates in the saturation region.

- (B) For  $R_{\rm C} = 3 \text{ k}\Omega$ , the BJT operates in the saturation region.

- (C) For  $R_{\rm C} = 20 \text{ k}\Omega$ , the BJT operates in the cut-off region.

- (D) For  $R_{\rm C} = 20 \text{ k}\Omega$ , the BJT operates in the linear region.

- 14. If the emitter resistance in a common-emitter voltage amplifier is not bypassed, it will [2014]

- (A) reduce both the voltage gain and the input impedance.

- (B) reduce the voltage gain and increase the input impedance.

- (C) increase the voltage gain and reduce the input impedance.

- (D) increase both the voltage gain and the input impedance.

- 15. A BJT in a common-base configuration is used to amplify a signal received by a 50  $\Omega$  antenna.

Assume kT/q = 25 mV. The value of the collector bias current (in mA) required to match the input impedance of the amplifier to the impedance of the antenna is \_\_\_\_\_\_. [2014]

16. For the common collector amplifier shown in the figure, the BJT has high  $\beta$ , negligible  $V_{\text{CE(sat)}}$ , and  $V_{\text{BE}} = 0.7$  V. The maximum undistorted peak-to-peak output voltage  $v_0$  (in Volts) is \_\_\_\_\_ [2014]

- 17. The built-in potential of an abrupt *p-n* junction is 0.75 V. If its junction capacitance  $(C_J)$  at a reverse bias  $(V_R)$  of 1.25 V is 5 pF, the value  $C_J$  (in pF) when  $V_R = 7.25$  V is \_\_\_\_\_. [2015]

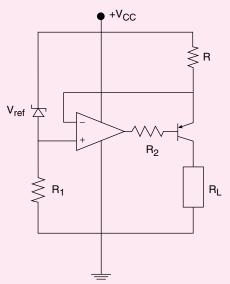

- **18.** Consider the constant current shown in the figure below. Let *b* represent the current gain of the transistor.

The load current  $I_0$  through  $R_L$  is

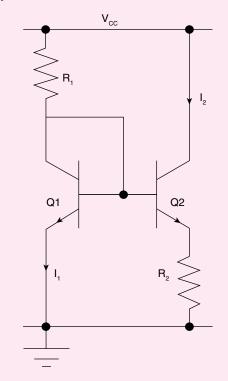

(A)  $I_0 = \left(\frac{\beta+1}{\beta}\right) \frac{V_{ref}}{R}$  (B)  $I_0 = \left(\frac{\beta}{\beta+1}\right) \frac{V_{ref}}{R}$ (C)  $I_0 = \left(\frac{\beta+1}{\beta}\right) \frac{V_{ref}}{2R}$  (D)  $I_0 = \left(\frac{\beta}{\beta+1}\right) \frac{V_{ref}}{2R}$  **19.** Resistor  $R_1$  in the circuit below has been adjusted so that  $I_1 = 1$  mA. The bipolar transistors Q1 and Q2 are perfectly matched and have very high current gain, so their base currents are negligible. The supply voltage  $V_{cc}$  is 6 V. The thermal voltage k T/q is 26 m V.

The value of  $R_2$  (in  $\Omega$ ) for which  $I_2 = 100 \ \mu$  A is

**20.** Consider the circuit shown in the figure. Assuming  $V_{\text{BE1}} = V_{\text{EB2}} = 0.7$  volt, the value of the dc voltage  $V_{\text{c2}}$  (in volt) is \_\_\_\_\_\_.

| Answer Keys               |              |                  |              |                |                |                  |              |              |              |

|---------------------------|--------------|------------------|--------------|----------------|----------------|------------------|--------------|--------------|--------------|

| Exercises                 |              |                  |              |                |                |                  |              |              |              |

| Practice Problems I       |              |                  |              |                |                |                  |              |              |              |

| 1. D                      | <b>2.</b> C  | <b>3.</b> B      | <b>4.</b> C  | 5. D           | <b>6.</b> A    | <b>7.</b> B      | 8. D         | 9. C         | 10. C        |

| 11. B                     | 12. A        | <b>13.</b> C     | 14. B        | 15. D          | 16. C          | 17. D            | <b>18.</b> B | <b>19.</b> D | <b>20.</b> D |

| <b>21.</b> B              | <b>22.</b> A | <b>23.</b> D     | <b>24.</b> B | <b>25.</b> B   |                |                  |              |              |              |

| Practice Problems 2       |              |                  |              |                |                |                  |              |              |              |

| 1. D                      | <b>2.</b> B  | 3. D             | <b>4.</b> A  | <b>5.</b> C    | 6. D           | <b>7.</b> C      | 8. D         | <b>9.</b> A  | 10. A        |

| <b>11.</b> A              | <b>12.</b> C | <b>13.</b> A     | 14. D        | <b>15.</b> C   | 16. A          | 17. A            | <b>18.</b> C |              |              |

| Previous Years' Questions |              |                  |              |                |                |                  |              |              |              |

| <b>1.</b> C               | <b>2.</b> B  | <b>3.</b> B      | <b>4.</b> A  | <b>5.</b> B    | <b>6.</b> B    | <b>7.</b> B      | <b>8.</b> C  | 9. D         | 10. C        |

| 11. B                     | 12. B        | <b>13.</b> B     | 14. B        | <b>15.</b> 0.5 | <b>16.</b> 9.4 | <b>17.</b> 2.4 t | o 2.6        | 18. B        |              |

| <b>19.</b> 598 Ω          |              | <b>20.</b> 0.5 V |              |                |                |                  |              |              |              |