# 7

## **Small Signal Analysis of FET**

## Multiple Choice Questions

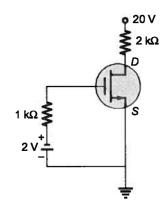

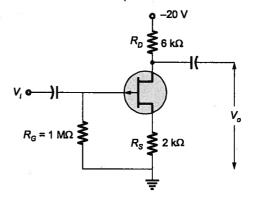

Q.1 The value of  $V_{GS}$  and  $V_{G}$  for the circuit shown in figure is

- (a) -2 V, -2 V

- (b) 2 V, -2 V

- (c) 2 V, -2 V

- (d) -2 V, 2 V

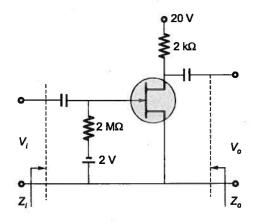

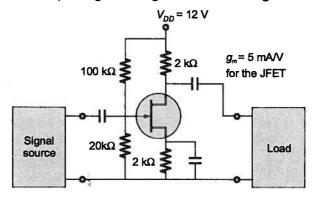

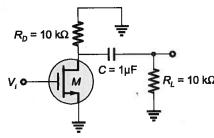

#### Common Data Questions (2 to 4):

Given:  $r_d = 20 \text{ k}\Omega$ ,  $I_{DSS} = 10 \text{ mA}$ ,  $V_p = -8 \text{ V}$

- Q.2  $Z_i$  and  $Z_o$  of the circuit are respectively

- (a)  $2 M\Omega$  and  $2 k\Omega$

- (b) infinity and  $2 M\Omega$

- (c)  $2 M\Omega$  and  $20/11 k\Omega$

- (d) infinity and 20/11 k $\Omega$

- Q.3  $I_D$  and  $V_{DS}$  under DC conditions are respectively

- (a) 5.625 mA and 8.75 V

- (b) 1.875 mA and 5 V

- (c) 4.5 mA and 11 V

- (d) 6.25 mA and 7.5 V

- Q.4 Tranconductance in milli siemens (ms) and voltage gain of the amplifier are respectively

- (a) 1.875 ms and 3.41

- (b) 1.875 ms and -3.41

- (c) 3.3 ms and -6

- (d) 3.3 ms and 6

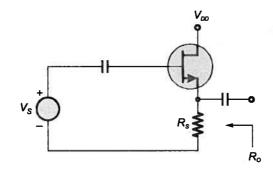

- Q.5 For the circuit shown below if  $g_m = 3 \times 10^{-3}$  and  $R_s = 3000 \Omega$ , then what is the value of  $R_o$ ?

- (a)  $3000 \Omega$

- (b)  $1000/3 \Omega$

- (c)  $300 \Omega$

- (d)  $100 \Omega$

[ESE-2006 (EE)]

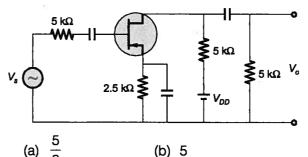

**Q.6** Given  $g_m = 2$  mA/V;  $r_d \rightarrow \infty$ . The voltage gain

$$|A_v| = \left| \frac{V_o}{V_S} \right|$$

is given by

- (c) 10

- (d)  $\frac{10}{3}$

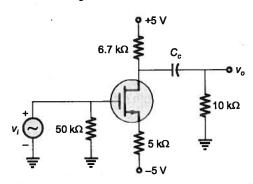

- Q.7 The mid-frequency input impedance of the JFET amplifier given in figure lies in the range

- (a)  $100-300 \Omega$

- (b) 1-3 kΩ

- (c)  $10-20 \text{ k}\Omega$

- (d) 100-200 kΩ

- Q.8 Consider a JFET amplifier shown below:

If  $g_m = 4000 \,\mu\text{U}$  then closed loop gain of amplifier is given by

- (a) 24

- (b) 12

- (c) 6.42

- (d) 2.66

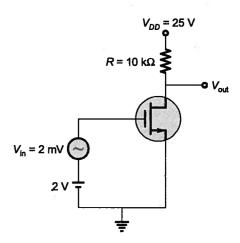

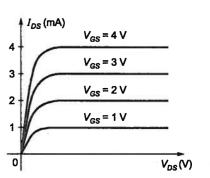

#### Common Data Questions (9 and 10):

Assume that that threshold voltage of the N channel MOSFET shown in figure is +0.75 V. The output characteristic of the MOSFET are also shown below:

- Q.9 The transconductance of the MOSFET is

- (a) 0.75 ms

- (b) 1 ms

- (c) 2 ms

- (d) 10 ms

- Q.10 The voltage gain of the amplifier is

- (a) +5

- (b) -7.5

- (c) +10

- (d) -10

- Q.11 The ac schematic of an NMOS common-source stage is shown in the figure below, where part of the biasing circuits has been omitted for simplicity. For the n-channel MOSFET M, the transconductance  $g_m = 1$  mAV, and body effect and channel length modulation effect are to be neglected. The lower cut-off frequency in Hz of the circuit is approximately is

- (a) 8

- (b) 32

- (c) 50

- (d) 200

[GATE-2013]

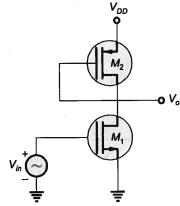

# Numerical Data Type Questions

Q.12 In the figure shown below:

If  $\mu_p = 1300 \text{ cm}^2/\text{V-sec}$ ;  $\mu_p = 325 \text{ cm}^2/\text{V-sec}$ ,

then the value of the (W/L) ratio  $\left(i.e.\frac{(W/L)_1}{(W/L)_2}\right)$

to make it a unity gain inverting amplifier is \_\_\_\_\_. (Assume  $V_A = \infty$ )

Q.13 Consider the circuit shown below. If the lower corner frequency due to coupling capacitor  $C_C$  is  $f_L = 20$  Hz, then the value of coupling capacitor  $C_c$  is \_\_\_\_  $\mu$ F.

Q.14 Consider a circuit shown in figure below. The transistor parameters are

$$V_{TP} = -2 \text{ V}$$

$$K_p = 0.25 \text{ mA/V}^2$$

$$+5 \text{ V}$$

$$3.2 \text{ k}\Omega$$

$$V_0$$

The value of 3 dB corner frequency (in MHz) due to capacitor  $C_L$  is \_\_\_\_\_.

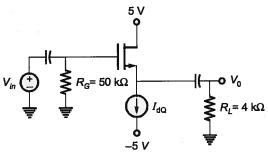

### Try Yourself

T1. For the source follower circuit shown in the figure below, the transistor parameters are  $V_T = 1 \text{ V}$ ,  $\frac{1}{2}\mu_n C_{ox} = 30 \text{ }\mu\text{A/V}^2$  and neglect channel length modulation. The small signal voltage gain to be  $A_v = \frac{V_0}{V_i} = 0.95$ . The value of  $\left(\frac{W}{L}\right)$  ratio if  $I_{dQ} = 4 \text{ mA}$  is

- (a) 50

- (b) 47

- (c) 28

- (d) 36