### Chapter 14. Semiconductor Electronics

### **Semiconductor, Diode and its Application**

#### **1 Mark Questions**

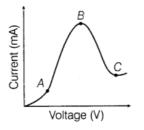

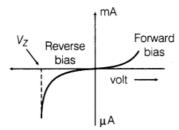

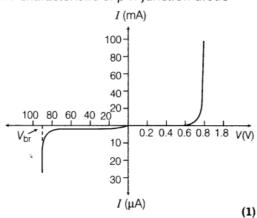

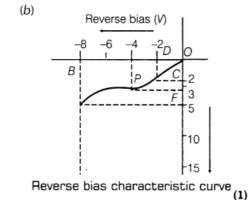

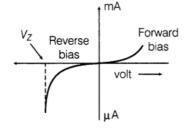

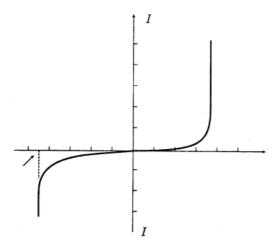

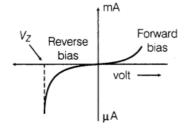

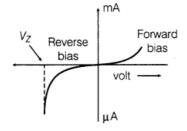

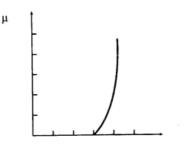

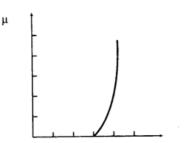

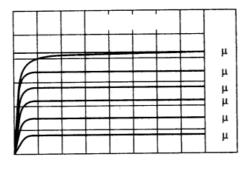

1. The graph shown in the figure represents a plot of current versus voltage for a given semiconductor. Identify the region, if any over which the semiconductor has a negative resistance. [All India 2013]

Ans. Resistance of a material can be found out by the slope of the curve V versus I. Part BC of the curve shows the negative resistance as with the increase in current and decrease in voltage.

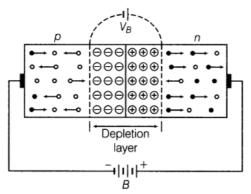

#### 2.What happens to the width of depletion layer of a p-n junction when it is (i)forward biased?

#### (ii)reverse biased? [All India 2011]

Ans.(i) Width of depletion layer's decreases in forward bias

(ii) Width depletion layer increases in reverse bias.

#### 3.Why cannot we take one slab of p-type semiconductor and physically join it to another

#### slab of n-type semiconductor to get p-n junction?

Ans. In this way, continuous contact cannot be produced at atomic level and junction will behave as a discontinuity for the flowing charge carrier.

#### 4. What is the most common use of photo diode? [All India 2009]

**Ans.** The photodiode can be used as a photodetector to detect optical signals

#### 5. State the relation between the frequency v of radiation emitted by LED and the band gap energy E, of the semiconductor used to fabricate it.[All India 2009 C]

Ans.Zener diode, which is used as a DC voltage regulator.

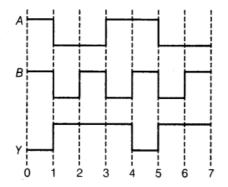

6.Figure show the I-V characteristics of a given device. Name the device and write where it is used.

Ans.

In LED, energy of the photon should be equal to or less than the band gap energy i.e.

$hv \le E_g$ where,  $E_g$  = band gap energy, v = frequency of emitted photon.

### 7.State the reason, why GaAs is most commonly used in making of a solar cell. [All India 2008]

**Ans**.solar radiation is nearly 1.5 eV. In order to have photo excitation, the energy of radiation (hv) must be greater than energy band gap ( $E_g$ ). Therefore, the semiconductor with energy band gap about 1.5 eV or lower than it and with higher absorption coefficient is likely to give better solar conversion efficiency. The energy band gap for Si is about 1.1 eV, while for GaAs, it is about 1.53 eV. The GaAs is better inspite of its higher band gap than Si because it absorbs relatively more energy from the incident solar radiations being of relatively higher absorption coefficient.

#### 8.At what temperature would an intrinsic semiconductor behave like a perfect insulator? [Delhi 2008 C]

Ans.At O° K temperature, an intrinsic semiconductor behaves like a perfect insulator

#### 9.Why should a photo diode be operated at reverse bias?[All India 2008]

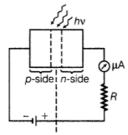

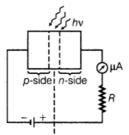

Ans. The photodiodes are used to detect the optical signals. The fraction change in minority

carrier in case of reverse biased diode is easily measurable than that of forward biased. That is why photodiode is operated at reverse bias.

#### **2 Marks Questions**

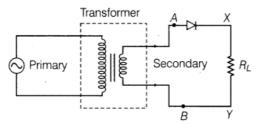

#### 10.Explain, with the help of a circuit diagram, the working of a p-n junction diode as a halfwave rectifier. [ah India 2014]

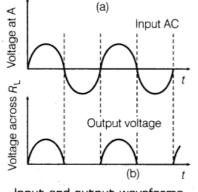

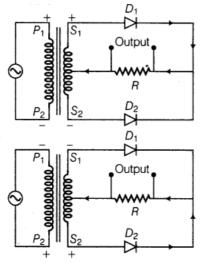

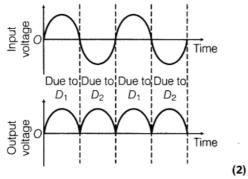

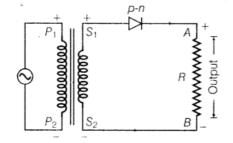

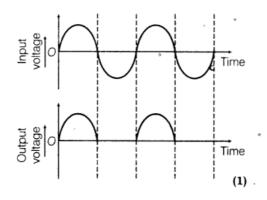

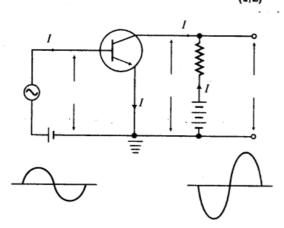

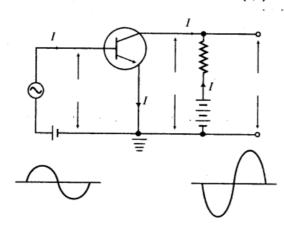

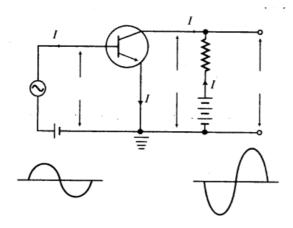

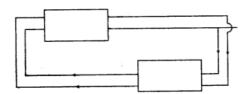

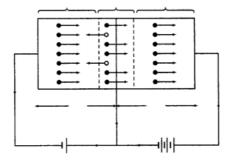

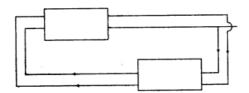

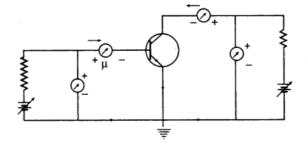

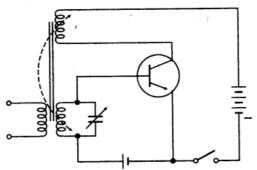

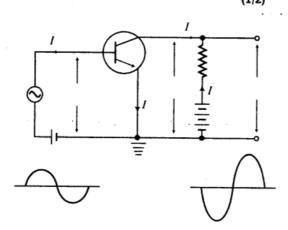

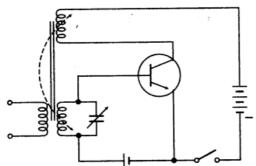

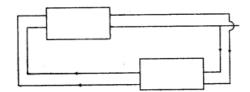

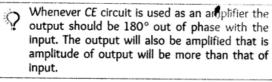

**Ans.p-n Junction Diode as a Half-Wave Rectifier** AC voltage to be rectified is connected to the primary coil of a step-down transformer. Secondary coil is connected to the diode through resistors Rj, across which output is obtained.

**Working** During positive half cycle of the input AC, the p-n junction is forward biased. Thus, the resistance in p-n junction becomes low and current flows. Hence, we get output in the load.

During negative half cycle of the input AC, the p-n junction is reverse biased. Thus, the resistance of p-n junction is high and current does not flow. Hence, no output in the load. So, for complete cycle of AC, current flows through the load resistance in the same direction.

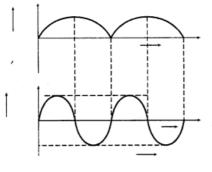

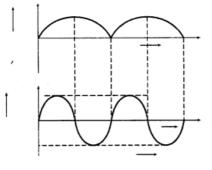

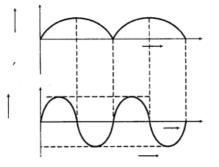

Input and output waveforms

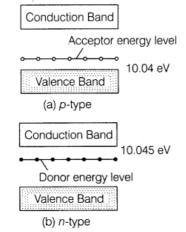

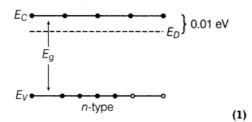

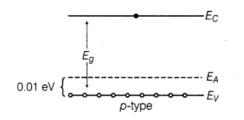

11.Draw energy band diagram of n-type and p-type semiconductor at temperature T > OK. Mark the donar and acceptor energy level with their energies. [Foreign 2014] Ans.

The required energy band diagram is shown below:

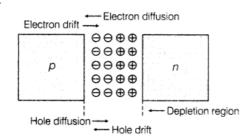

12. Distinguish between a metal and an insulator on the basis of energy band diagram.

#### [Foreign 2014]

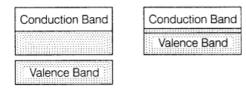

**Ans**.(i) **Metal** For metals, the valence band is completely filled and the conduction band can have two possibilities either it is partially filled with an extremely small energy gap between the valence and conduction bands or it is empty, with two bands overlapping each other as shown below:

(ii) On applying an small even electric field, metals can conduct electricity.

(i) **Insulators :** for insulator, the energy gap between the conduction and valence bands are very large, also the conduction band is practically empty, as shown below:

(ii) When an electric field is applied across such a solid, the electrons find it difficult to acquire. So, a large amount of energy is required to reach the conduction band. Thus, the conduction band continues to be empty. That is why no current flows through insulators.

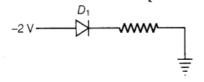

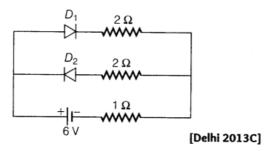

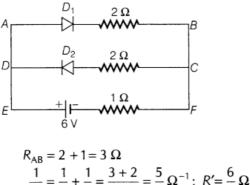

13. Assuming that the two diodes  $D_1$  and  $D_2$  used in the electric circuit shown in the figure are ideal, find out the value of the current flowing through  $1 \Omega$  resistor.

Ans.

According to the question

$$\frac{1}{R'} = \frac{1}{2} + \frac{1}{3} = \frac{1}{6} - \frac{1}{6} + \frac{1}{6} + \frac{1}{5} + \frac{1$$

14.Explain the term 'drift velocity' of electrons in conductor. Hence, obtain an expression for the current through a conductor in terms of 'drift velocity'.[All India 2013] Ans.'Drift velocity' of electrons in a conductor

Metals contain a large number of free electrons. These electrons are in continuous random

motion. Due to the random motion, the free electrons collide with positive metal ions with high frequency and undergo change in direction at each collision. So, the average velocity for the electrons in a conductor is zero.Now, when this conductor is connected to a source of emf, an electric field is established in the conductor, such that E = V/L

where, V = potential difference across the conductor and L = length of the conductor. The electric field exerts an electrostatic force -Ee on each free electron in the conductor. The acceleration of each electron is given by

$$\mathbf{a} = -\frac{\mathbf{e}\mathbf{E}}{m}$$

where, e = electric charge on electron and m = mass of electron.

The average velocity of all the free electrons in the conductor is called the drift velocity of free electrons of the conductor.

$$\mathbf{v}_d = -\frac{e\mathbf{E}}{m}\tau \qquad \dots (\mathbf{i})$$

where,  $\tau$  = relaxation time between two successive collisions.

Thus, the expression for the drift velocity is electric field.

$$E = -\frac{V}{L} \qquad \dots (ii)$$

Let n = number density of electrons in the conductor.

Number of free electrons in the conductor = *nAL*

Total charge on the conductor, q = nALeTime taken by this charge to cover the length *L* of the conductor,  $t = L / v_d$

Current,  $I = \frac{q}{t} = \frac{nALe}{L} \times v_d$

Using Eqs. (i) and (ii), we get that

$$I = nAe \times \left(-\frac{eE}{m}\tau\right) = nAe \times \left(-\frac{e(-V)}{mL}\tau\right)$$

$$I = \left(\frac{ne^{2}A}{mL}\tau\right)V$$

(1)

15.Mention the important considerations required while fabricating a p-n junction diode to be used as a Light Emitting Diode (LED). What should be the order of band gap of an LED, if it is required to emit light in the visible range? [Delhi 2013] Ans. For LEDs, the threshold voltages are much higher and slightly different for different colours. The reverse breakdown voltages of LEDs are low generally around 5V. It is due to this reason, the care is taken that high reverse voltages do not appear across LEDs. There is very little resistance to limit the current in LED. Therefore, a resistor must be used in series with the LED to avoid any damage to it. (1) The semiconductor used for fabrication of visible LEDs must at least have a band gap of 1.8eV (spectral range of visible light is from about 0.4 µm to 0.7 µm i.e. from about 3 eV to 1.8 eV). (1)

## 16.Write two characteristics features to distinguish between n-type and p-type semiconductors. [All India 2012]

Ans.

(i) In *n*-type semiconductor, the semiconductor is doped with pentavalent impurity. In it the electrons are majority carriers and holes are minority carriers or  $n_e >> n_h$  ( $n_e$ = number density of electrons,  $n_h$ = number density of holes). In energy band diagram of *n*-type semiconductor, the donor energy level  $E_D$  is slightly below the bottom of  $E_C$  conduction band and thus, the electron can move to conduction band, even with small supply of energy.

(ii) In *p*-type semiconductor, the semiconductor is doped with trivalent impurity. In this semiconductor, the holes are the majority carriers and electrons are the minority carriers i.e.  $n_h >> n_e$ .

In energy-band diagram of *p*-type, the acceptor energy level is slightly above the top of valence band  $E_V$ . Thus, even with small supply of energy electron from valence band can jump to level,  $E_A$  and ionize the acceptor, negatively.

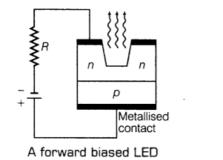

**Ans.** When we apply sufficient voltage to LED, electron move across the junction into p-region and get attracted to the holes there. Thus, electrons and holes recombine. During each recombination, the electric potential energy is converted into the electromagnetic energy and a photon of light with a characteristic frequency is emitted, this is how, LED works. Advantages of LEDs over incandescent lamps

(i) Since, LEDs do not have a filament that can burn out, hence, they last longer.

They do not get hot during use.

- (*i*) Since, LEDs do not have a filament that can burn out, hence, they last longer.

- (ii) They do not get hot during use.

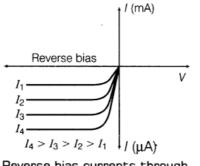

18. The current in the forward bias is known to be more ( $\sim$  mA) than the current in the reverse bias ( $\sim \mu A$ ). What is the reason, to operate the photodiode in reverse bias? [Delhi 2012]

**Ans**.When photo diode is illuminated with light due to breaking of covalent bonds, equal number of additional electrons and holes comes into existence whereas fractional change in minority charge carrier is much higher than fractional change in majority charge carrier. Since, the fractional change of minority carrier current is measurable significantly in reverse bias than that of forward bias. Therefore, photo diode are connected in reverse bias.

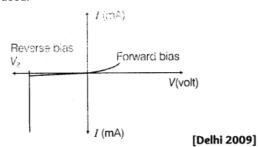

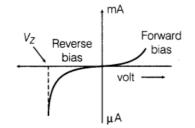

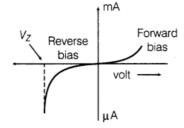

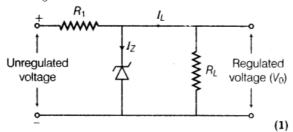

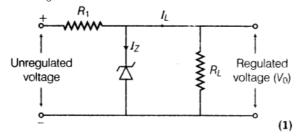

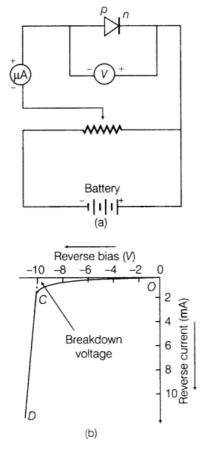

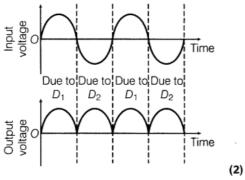

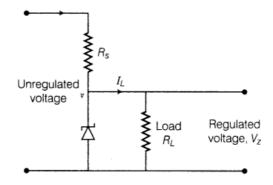

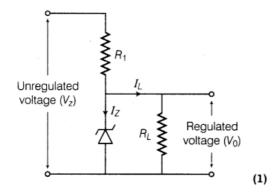

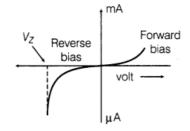

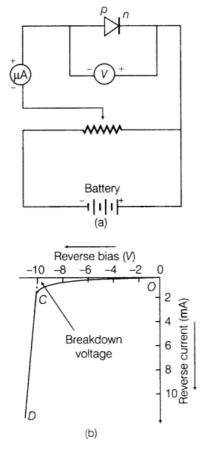

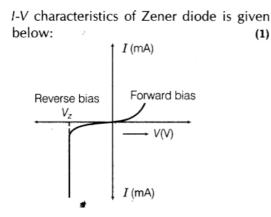

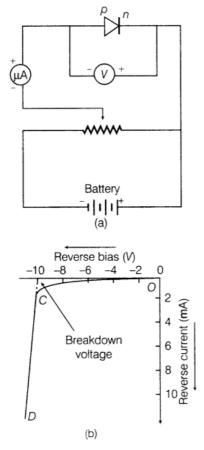

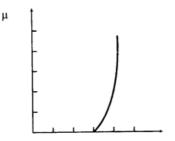

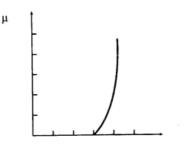

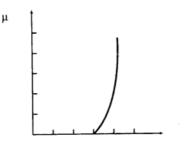

## 19.Name the semiconductor device that can be used to regulate an unregulated DC power supply. With the help of 7-V characteristics of this device, explain its working principle. [Delhi 2011]

**Ans**. Zener diode is used as voltage regulator.

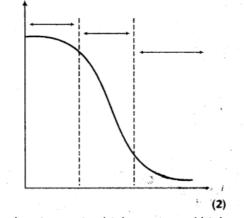

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

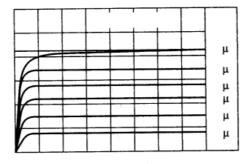

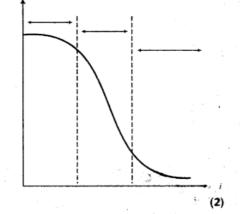

Characteristic of a Zener diode

## 20.How is forward biasing different from reverse biasing in a p-n junction diode? [Delhi 2011]

Ans.Differences between forward and reverse biases are given below:

| Forward bias                                                                                                       | Reverse bias                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Positive terminal of battery is connected to <i>p</i> -type and negative terminal to <i>n</i> -type semiconductor. | Positive terminal of<br>battery connected to<br><i>n</i> -type and negative<br>terminal to <i>p</i> -type<br>semiconductor. |

| Depletion layer is very thin.                                                                                      | Depletion layer is thick.                                                                                                   |

| <i>p-n</i> junction offers very low resistance.                                                                    | <i>p-n</i> junction offers very high resistance.                                                                            |

| An ideal diode have zero resistance.                                                                               | An ideal diode have<br>infinite resistance.                                                                                 |

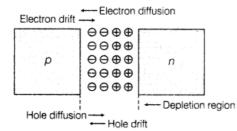

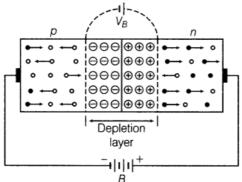

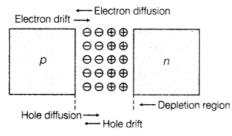

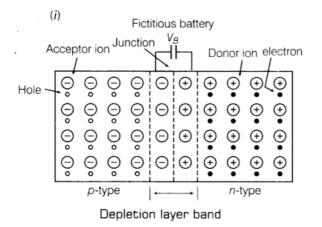

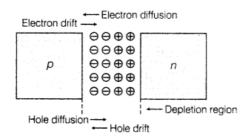

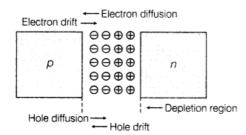

#### 21.Explain, how a depletion region is formed in a junction diode?[Delhi 2011]

**Ans.** With the formation of p-n junction, the holes from p-region diffuse into the n-region and electrons from n-region diffuse into p-region and electron-hole pair combine and get annihilated.

This input produces potential barrier,  $V_B$  across in junction which opposes the further diffusion through the junction. Thus, small region forms in the vicinity of the junction which is depleted of free charge carrier and has only immotile ions is called the depletion region.

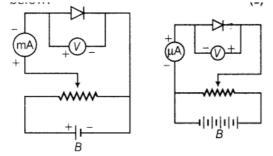

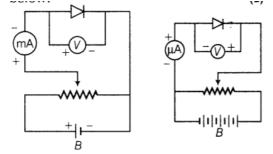

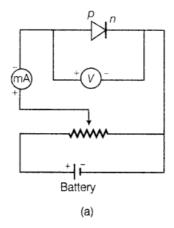

#### 22.Draw the circuit diagram showing how a p-n junction diode is

#### (i)forward biased

#### (ii)reverse biased.

#### How is the width of depletion layer affected in the two cases?[All India 2011 C]

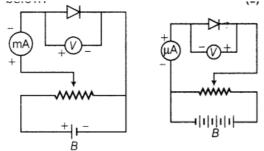

Ans.Circuit diagram of forward biased and reverse biased p-n junction diode is shown

The width of depletion layer (i) decreases in forward bias. (ii) increases in reverse bias.

## 23.Carbon and silicon both have four valence electrons each, then how are they distinguished? [Delhi 2011 c]

**Ans**. The four valence electrons of carbon are present in second orbit while that of silicon in third orbit. So, energy required to extricate an electron from silicon is much smaller than carbon.

Therefore, the number of free electrons for conduction in silicon is significant on contrary of carbon. This makes silicon conductivity much higher than carbon. This is the main distinguishable property.

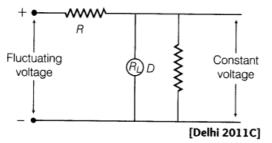

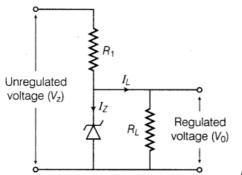

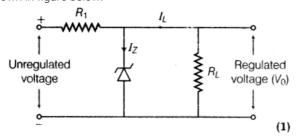

**24.** Name the device, *D* which is used as a voltage regulator in the given circuit and give its symbol.

Ans.

Device, *D* is a Zener diode. Symbol of Zener diode

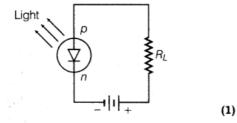

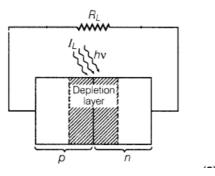

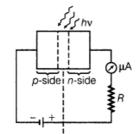

25.Draw the circuit diagram of an illuminated photo diode in reverse bias. How is photo diode used to measure light intensity? [Delhi 2010]26.Write the main use of the (i)photo diode

#### (ii)Zener diode. [All India 2010 c]

Ans. Circuit diagram of illuminated photo diode in reverse bias is shown below:

A reverse biased photodiode

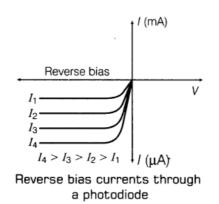

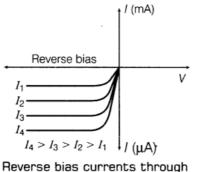

Hence, frequency of light v such that  $hv > E_g$ , where  $E_g$  is band gap of increasing intensity  $I_1$ ,  $I_2$ ,  $I_3$ , etc. The value of reverse saturation current increases with the increase of intensity of light.

| Thus, the measurement of charge in  | the |

|-------------------------------------|-----|

| reverse saturation current can give | the |

| intensity of incident light.        | (1) |

### 26.Write the main use of the (i) photo diode (ii) Zener diode [All India 2010 c] Ans.Main use of photo diode In demodulation of optical signal and detection of optical signal.

Main use of Zener diode As DC voltage regulator.

**27.** Distinguish between an intrinsic semiconductor and *p*-type semiconductor. Give reason, why a *p*-type semiconductor crystal is electrically neutral, although  $n_h >> n_e$ ? [Delhi 2008C]

Ans.Differences between intrinsic and p-type semiconductors are given below:

| Intrinsic<br>semiconductor                       | p-type semiconductor                                                             |

|--------------------------------------------------|----------------------------------------------------------------------------------|

| Pure semiconductor<br>of tetravalent<br>crystal. | Impure semiconductor of<br>tetravalent crystal doped<br>with trivalent impurity. |

| $n_e = n_h$                                      | n <sub>e</sub> < n <sub>h</sub>                                                  |

| Conductivity<br>depends on<br>temperature.       | Conductivity depends on temperature as well as dopant concentration.             |

In p-type semiconductor, trivalent impurity is doped with tetravalent pure semiconductor. Both type of atom (impurity and host semiconductor) are electrically neutral and hence, so produced p-type semiconductor is electrically neutral

## 28.Draw a circuit diagram showing the biasing of an LED. State the factor which controls (i)wavelength of light.

(1)

#### (ii) intensity of light emitted by the diode. [Foreign 2008]

Ans. Circuit diagram of a forward biased LED is shown below:

- (i) Wavelength of light is controlled by band gap (Eg) of semiconductor material.

- (*ii*) Intensity of light emitted by the diode depends on concentration of impurity in junction diode. (1)

29.How is that the reverse current in a Zener diode starts increasing suddenly at a relatively low breakdowns voltage of 5 V or so?[All India 2008 C] Ans.

In Zener diode, the depletion layer width is very small (<  $10^{-7}$  m) and hence even a very small breakdown voltage of 5 V, set up a high electric field  $5 \times 10^7$  V/m which facilitating of breaking of covalent band and liberation of electrons drifted towards *n*-type semiconductor. It produces large reverse current. (2)

30.Draw the (i) symbol and (ii) the reverse I-V characteristics of a Zener diode. Explain briefly, which property of the characteristics enables us to use Zener diode as voltage regulator. [All India 2008 C]

Ans. Zener diode is used as voltage regulator.

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

Device, D is a Zener diode.

Symbol of Zener diode

#### **3 Marks Questions**

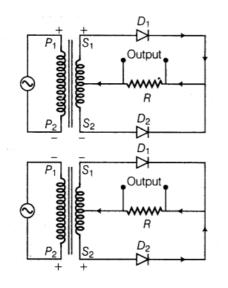

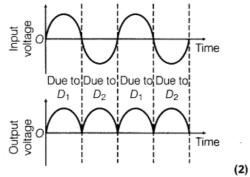

31.Write any two distinguishing features between conductors, semiconductors and insulators on the basis of energy band diagrams. [All India 2014]32.Draw the circuit diagram of a full-wave rectifier using p-n junction diode. Explain its working and show the output input waveforms. [Delhi 2012]

#### Ans.

Differences between conductor, insulator and semiconductor on the basis of energy bands are given below:

| Conductor (Metal)                                                                                                                                                                                                                    | Insulator                                                                                                                                                                                                                                     | Semiconductor                                                                                                                                                                                                                                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| In conductor, either there is no energy<br>gap between the conduction band<br>which is partially filled with electrons<br>and valence band or the conduction<br>band and valence band overlap each<br>other.                         | In insulator, the valence band is<br>completely filled, the conduction<br>band is completely empty and<br>energy gap is quite large that<br>small energy from any other<br>source cannot overcome it.                                         | In semiconductor also, like insulators<br>the valence band is totally filled and<br>the conduction band is empty but<br>the energy gap between conduction<br>band and valence band, unlike<br>insulators is very small.                                                                       |  |

| Thus, many electrons from below the<br>fermi level can shift to higher energy<br>levels above the fermi level in the<br>conduction band and behave as free<br>electrons by acquiring a little more<br>energy from any other sources. | Thus, electrons are bound to<br>valence band and are not free<br>to move and hence, electric<br>conduction is not possible in<br>this type of material.                                                                                       | Thus, at room temperature, some<br>electrons in the valence band<br>acquire thermal energy greater<br>than energy band gap and jump<br>over to the conduction band where<br>they are free to move under the<br>influence of even a small electric<br>field and acquire small<br>conductivity. |  |

| lectron Conduction Conduction<br>hergy E <sub>C</sub><br>E <sub>V</sub><br>Valence band Company<br>For metals                                                                                                                        | Empty conduction band<br>$\widehat{B}_{g}^{\dagger} \stackrel{E_{C}}{=} \underbrace{\downarrow}_{E_{g} > 3 \text{ eV}}_{Valence}$<br>$\widehat{B}_{g}^{\dagger} \stackrel{E_{C}}{=} \underbrace{\downarrow}_{E_{g} > 3 \text{ eV}}_{Valence}$ | $E_{g} < 3 \text{ eV}$                                                                                                                                                                                                                                                                        |  |

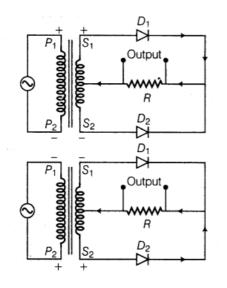

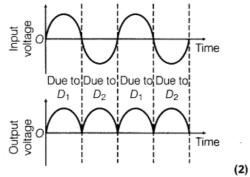

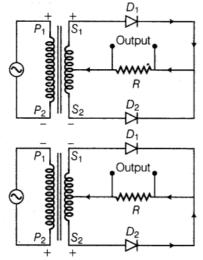

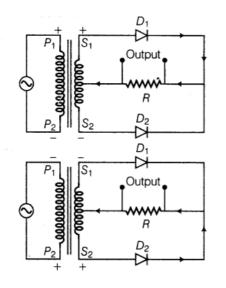

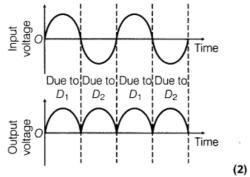

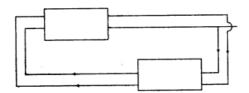

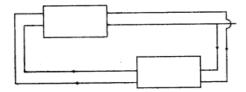

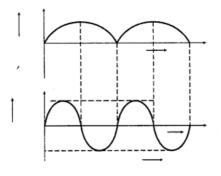

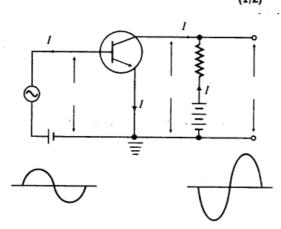

32.Draw the circuit diagram of a full-wave rectifier using p-n junction diode. Explain its working and show the output input wave forms. [Delhi 2012]

Ans.

In these type of questions, we have to mind that in full-wave rectifier, full cycle of the input will be used.

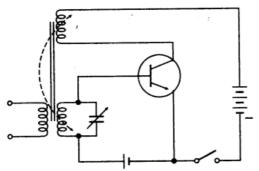

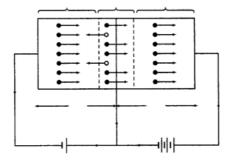

The circuit diagram of full-wave rectifier is shown below:

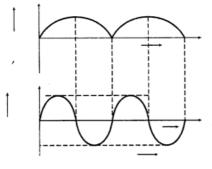

The input and output waveforms have been given below:

Its working based on the principle that junction diode offer very low resistance in forward bias and very high resistance in reverse bias. (1)

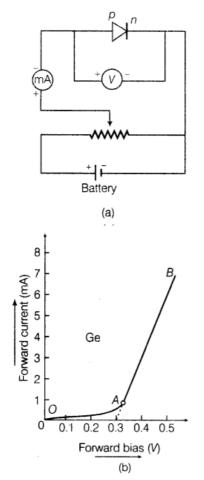

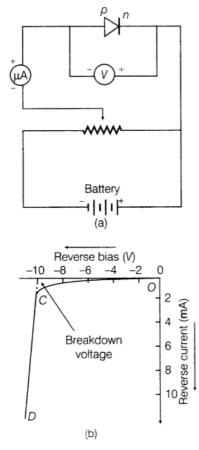

33.Draw V-I characteristics of a p-n junction diode. Answer the following questions, giving reasons.

(i)Why is the current under reverse bias almost independent of the applied potential up to a critical voltage?

(ii)Why does the reverse current show a sudden increase at the critical voltage?

Name any semiconductor device which operates under the reverse bias in the breakdown region.

[All India 2012] Ans.

V-I characteristic of p-n junction diode

(i)Under the reverse bias condition, the holes of p-side are attracted towards the negative terminal of the battery and the electrons of the n-side are attracted towards the positive

terminal of the battery. This increases the depletion layer and the potential barrier. However, the minority charge carriers are drifted across the junction producing a small current. At any temperature, the number of minority carriers is constant, so there is the small current at any applied potential. This is the reason for the current under reverse bias to be almost'independent of applied potential. At the critical voltage, avalanche breakdown takes place which results in a sudden flow of large current.

(ii) At the critical voltage, the holes in the n-side and conduction electrons in the p-side are accelerated due to the reverse bias voltage. These minority carriers acquire sufficient kinetic energy from the electric field and collide with a valence electron.

Thus, the bond is finally broken and the valence electrons move into the conduction band resulting in enormous flow of electrons and thus, formation of hole-electron pairs. Thus, there is a sudden increase in the current at the critical voltage.

Zener diode is a semiconductor device which operates under the reverse bias in the breakdown region.

## 34.Draw a labelled diagram of a full -wave rectifier circuit. State its working principle. Show the input-output wave forms.[All India 2011]

#### Ans.

In these type of questions, we have to mind that in full-wave rectifier, full cycle of the input will be used.

The circuit diagram of full-wave rectifier is shown below:

The input and output waveforms have been given below:

Its working based on the principle that junction diode offer very low resistance in forward bias and very high resistance in reverse bias. (1)

35.Name the important processes that occurs during the formation of a p-n junction.Explain briefly, with the help of asuitable diagram, how a p-n junction is formed.Define the term 'barrier potential'?[Foreign 2011] Ans.

During formation of p-n junction, diffusion of charge takes place. As, soon as p-type semiconductor is joined with n-type semiconductor, diffusion of free charges across the junction starts.

#### For explanation of formation p-n junction

With the formation of p-n junction, the holes from p-region diffuse into the n-region and electrons from n-region diffuse into p-region and electron-hole pair combine and get annihilated.

This input produces potential barrier,  $V_B$  across in junction which opposes the further diffusion through the junction. Thus, small region forms in the vicinity of the junction which is depleted of free charge carrier and has only immotile ions is called the depletion region.

Potential barrier The potential distribution near the p-n junction is known as potential barrier

#### 36.(i) Why is a photo diode operated in reverse bias mode? (ii)For what purpose is a photo diode used?

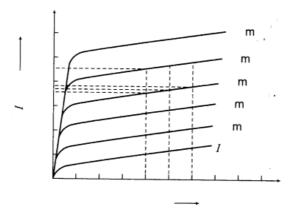

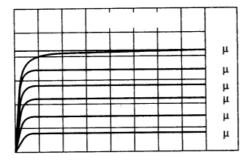

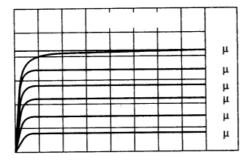

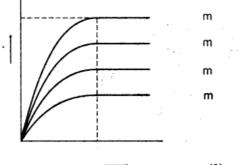

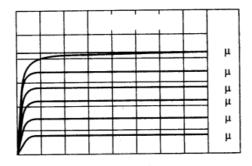

## (iii)Draw its I-V characteristics for different intensities of illumination. [HOTS; All India 2011 C]

Ans.

In these type of questions, we should mind that the diode is connected reverse biased or forward biased.

(i) Photo diode is connected in reverse bias and feeble reverse current flows due to thermally generated electron-hole pair, known as dark current. When light of

suitable frequency (v) such that  $hv > E_g$ , where  $E_g$  is band gap is incident on diode, additional electron-hole pair generated and current grows in the circuit.(1)

(ii)Main use of photo diode In demodulation of optical signal and detection of optical signal.

(iii)Circuit diagram of illuminated photo diode in reverse bias is shown below:

A reverse biased photodiode

Reverse bias currents through a photodiode

Hence, frequency of light v such that  $hv > E_g$ , where  $E_g$  is band gap of increasing intensity  $l_1$ ,  $l_2$ ,  $l_3$ , etc. The value of reverse saturation current increases with the increase of intensity of light.

Thus, the measurement of charge in the reverse saturation current can give the intensity of incident light. (1)

#### 37.(i)Why are Si and GaAs preferred materials for solar cells?

## (ii)Describe briefly with the help of a necessary circuit diagram, the working principle of a solar cell.[All India 2011 C]

**Ans**. (i) solar radiation is nearly 1.5 eV. In order to have photo excitation, the energy of radiation (hv) must be greater than energy band gap ( $E_g$ ). Therefore, the semiconductor with energy band gap about 1.5 eV or lower than it and with higher absorption coefficient is likely to give better solar conversion efficiency. The energy band gap for Si is about 1.1 eV, while for GaAs, it is about 1.53 eV. The GaAs is better inspite of its higher band gap than Si because it absorbs relatively more energy from the incident solar radiations being of relatively higher absorption coefficient.

(*ii*) When light of frequency, v such that  $hv > E_g$  (band gap) is incident on junction, then electron-hole pair liberated in the depletion region drifts under the influence of potential barrier. The gathering of these charge carriers make *p*-type as positive electrode and *n*-type as negative electrode and hence, generating photo-voltage across solar cell.

38.(i) Describe the working of Light Emitting Diodes (LEDs).(ii)Which semiconductors are preferred to make LEDs and why?(iii)Give two advantages of using LEDs over conventional incandescent low power lamps.[All India 2011]

**Ans.**(i) Working of LED LED is a forward biased p-n junction which converts electrical energy into optical energy of infrared and visible light region.

Being in forward bias, thin depletion layer and low potential barrier facilitate diffusion of

electron and hole through the junction when high energy electron of conduction band combines with the low energy holes in valence band, then energy is released in the form of photon, may be seen in the form of light.

(ii) Semiconductors with appropriate band gap ( $E_g$ ) close to 1.5 eV are preferred to make LED size GaAs, CdTe, etc.the other reasons to select these materials e high optical absorption, availability of raw material and low cost

(iii) Uses of LEDs (a) LED can operate at very low voltage and consumes less power in comparison to incandescent lamps

(b) Unlike the lamps, they take very less operational time and have long life.

## 39.With the help of a suitable diagram, explain the formation of depletion region in a p-n junction. How does its width change when the junction is (i)forward biased and

#### (ii)reverse biased? [All India 2009]

**Ans.** With the formation of p-n junction, the holes from p-region diffuse into the n-region and electrons from n-region diffuse into p-region and electron-hole pair combine and get annihilated.

This input produces potential barrier,  $V_B$  across in junction which opposes the further diffusion through the junction. Thus, small region forms in the vicinity of the junction which is depleted of free charge carrier and has only immotile ions is called the depletion region.

Circuit diagram of forward biased and reverse biased p-n junction diode is shown

The width of depletion layer (i) decreases in forward bias. (ii) increases in reverse bias.

## 40.(i) With the help of circuit diagrams, distinguish between forward biasing and reverse biasing of p-n junction diode.

(ii)Draw V-I characteristics of a p-n junction diode in

(a)forward bias.

(b) and bias and bia

(b)reverse bias. [AH India 2009]

The width of depletion layer (a) decreases in forward bias.

(b) increases in reverse bias.

(ii)(a)Differences between forward and reverse biases are given below:

| Forward bias                                                                                                       | <b>Reverse bias</b>                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Positive terminal of battery is connected to <i>p</i> -type and negative terminal to <i>n</i> -type semiconductor. | Positive terminal of<br>battery connected to<br><i>n</i> -type and negative<br>terminal to <i>p</i> -type<br>semiconductor. |

| Depletion layer is very thin.                                                                                      | Depletion layer is thick.                                                                                                   |

| <i>p-n</i> junction offers very low resistance.                                                                    | <i>p-n</i> junction offers very high resistance.                                                                            |

| An ideal diode have zero resistance.                                                                               | An ideal diode have<br>infinite resistance.                                                                                 |

At the critical voltage, the holes in the n-side and conduction electrons in the p-side are accelerated due to the reverse bias voltage. These minority carriers acquire sufficient kinetic energy from the electric field and collide with a valence electron.

Thus, the bond is finally broken and the valence electrons move into the conduction band resulting in enormous flow of electrons and thus, formation of hole-electron pairs. Thus, there is a sudden increase in the current at the critical voltage.

Zener diode is a semiconductor device which operates under the reverse bias in the breakdown region.

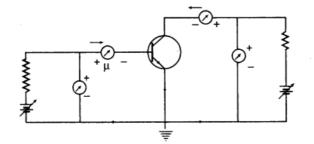

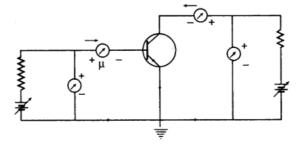

## 41.Explain with the help of a circuit diagram how a Zener diode works as a DC voltage regulator? Draw its I-V characteristic s.[All India 2009]

Ans. Zener diode is used as voltage regulator.

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

## 42. How is a Zener diode fabricated so as to make it a special purpose semiconductor diode? Draw the circuit diagram of a Zener diode as a voltage regulator and explain its working. [All India 2009 C]

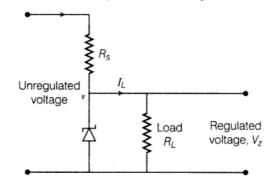

**Ans**.Zener diode fabrication Zener diode is made by heavily doping of both p and n-type semiconductors and hence, the width of depletion layer becomes thin which lead to produce large electric field to increase the current even on applying reverse voltage of 4 or 5 V. (i)Zener diode is used as voltage regulator.

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

(ii) From the figure, it is clear that the device, X is a full-wave rectifier. Circuit diagram as shown in figure below:

Zener diode connected with unregulated DC voltage in reverse bias. When the input voltage increases, then current through R, increase and hence, voltage drop across  $R_p$  increases while voltage across the Zener diode remains constant. The voltage across Zener diode remains constant beyond Zener voltage and hence, same/constant regulated voltage is obtained across  $R_L$ .

(iii) In n-type semiconductor,

$n_e > n_h$  ...(i) On incidence of light of suitable frequency, there is equal rise in number of electrons and holes [i.e.  $\Delta n$  (say)]  $\Rightarrow \qquad \frac{1}{n_e} < \frac{1}{n_h} \text{ or } \frac{\Delta n}{n_e} < \frac{\Delta n}{n_h}$ where,  $\Delta n$  = change in electron or hole charge carrier.

Thus, fractional change in minority charge carrier (hole) is much higher than fraction change in majority charge carrier (electron). Also, minority charge carrier contribute in drift current in reverse bias.

Thus, with incidence of light, fractional change in minority charge carrier is significant. Therefore, photo diode should be connected in reverse bias for measuring light intensity.

43. The figure below, shows the V-I characteristics of a semiconductor diode.

(i)Identify the semiconductor diode used.

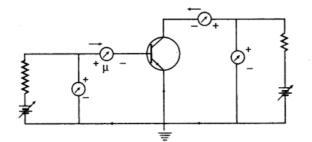

(ii) Draw the circuit diagram to obtain the given characteristic of this device.

(iii) Briefly explain, how this diode can be used as a voltage regulator.[Delhi 2008] Ans.(i) Zener diode

(ii) From the figure, it is clear that the device, X is a full-wave rectifier. Circuit diagram as shown in figure below:

Zener diode connected with unregulated DC voltage in reverse bias. When the input voltage increases, then current through R, increase and hence, voltage drop across  $R_p$  increases while voltage across the Zener diode remains constant. The voltage across Zener diode remains constant beyond Zener voltage and hence, same/constant regulated voltage is obtained across  $R_l$ .

(iii) Zener diode is used as voltage regulator.

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

#### **5Marks Questions**

44.(i)State briefly the processes involved in the formation of p-n junction, explaining clearly how the

depletion region is formed.

(ii)Using the necessary circuit diagrams, show how the V-I characteristics of a p-n junction are obtained in (a) forward biasing (b) reverse biasing How are these characteristics made use of in rectification? [Delhi 2014]

**Ans**.(i) **p-n Junction** A p-n junction is an arrangement made by a close contact of n-type semiconductor and p-type semiconductor. There are various methods of forming p-n junction diode. In one method, an n-type germanium crystal is cut into thin slices called wafers. An aluminium film is laid on an n-type wafer which is then heated in an oven at a temperature of

about 600°C. Aluminium then diffuses into the surface of wafer. In this way, a p-type semiconductor is formed on n-type semiconductor.

**Formation of Depletion Region in p-n Junction** In an n-type semiconductor, the concentration of electrons is more than concentration of holes. Similarly, in a p-type semiconductor, the concentration of holes is more than that of concentration of electrons. During formation of p-n junction and due to the concentration gradient across p and n-sides, holes diffuse from p-side to n-side (p-> n) and electrons diffuse from n-side to p-side (n -> p).

The diffused charge carriers combine with their counterparts in the immediate vicinity of the junction and neutralise each other, (I) Thus, near the junction, positive charge is built on n-side and negative charge on p-side This sets up potential difference across the junction and an internal electric field Ej directed from n-side to p-side. The equilibrium is established when the field £, becomes strong enough to stop further diffusion of the majority charge carriers (however, it helps the minority charge carriers to diffuse across the junction). The region on either side of the junction which becomes depleted (free) from the mobile charge carriers is called depletion region or **depletion layer**. The width of depletion region is of the order of 10<sup>-6</sup> m. The potential difference developed across the depletion region is called the potential barrier. Potential barrier depends on dopant concentration in the semiconductor and temperature of the junction.

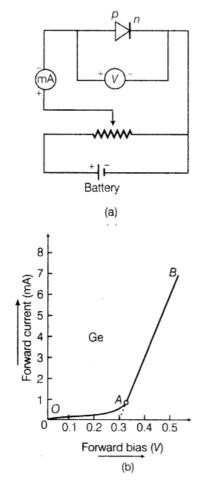

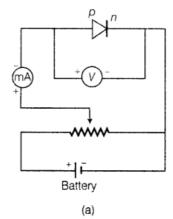

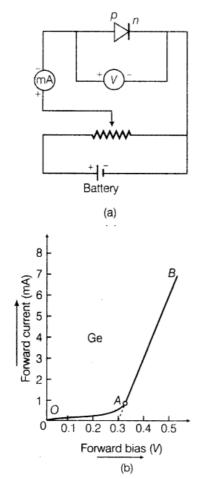

#### (ii) (a) Forward Biased Characteristics

The circuit diagram for studying forward biased characteristics is shown in the figure. Starting from a low value, forward bias voltage is increased step by step (measured by voltmeter) and forward current is noted (by ammeter). A graph is plotted between voltage and current. The curve so obtained is the forward characteristic of the diode.

At the start when applied voltage is low, the current through the diode is almost zero. It is because of the potential barrier, which opposes the applied voltage. Till the applied voltage exceeds the potential barrier, the current increases very slowly with increase in applied voltage (OA portion of the graph). With further increase in applied voltage, the current increases very rapidly (AB portion of the graph), in this situation, the diode behaves like a conductor. The forward voltage beyond which the current through the junction starts increasing rapidly with voltage is called knee voltage. If line AB is extended back, it cuts the voltage axis at potential barrier voltage.

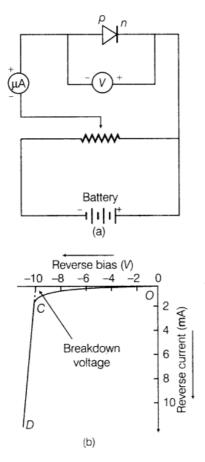

#### (b) Reverse Biased Characteristics

The circuit diagram for studying reverse biased characteristics is shown in the figure.

In reverse biased, the applied voltage supports the flow of minority charge carriers across the junction. So, a very small current flows across the junction due to minority charge carriers. Motion of minority charge carriers is also supported by internal potential barrier, so all the minority carriers cross over the junction. Therefore, the small reverse current remains almost constant over a sufficiently long range of reverse bias, increasing very little with increasing voltage (OC portion of the graph). This reverse current is voltage independent upto certain voltage known as **breakdown voltage** and this voltage independent current – is called reverse

saturation current.

#### Use of p-n Junction Characteristics in Rectification

From forward and reverse characteristics, it is clear that current flows through the junction diode only in forward bias not in reverse bias i.e. current flows only in one direction

45.(a) Draw the circuit arrangement for studying the V-I characteristics of a p-n junction diode in (i) forward and (ii) reverse bias. Briefly explain how the typical V- I characteristics of a diode are obtained and draw these characteristics.

#### (b)With the help of necessary circuit diagram, explain the working of a photo diode used for detecting optical signals. [All India 2014 C]

####

The circuit diagram for studying forward biased characteristics is shown in the figure. Starting from a low value, forward bias voltage is increased step by step (measured by voltmeter) and forward current is noted (by ammeter). A graph is plotted between voltage and current. The curve so obtained is the forward characteristic of the diode.

At the start when applied voltage is low, the current through the diode is almost zero. It is because of the potential barrier, which opposes the applied voltage. Till the applied voltage exceeds the potential barrier, the current increases very slowly with increase in applied voltage (OA portion of the graph). With further increase in applied voltage, the current increases very rapidly (AB portion of the graph), in this situation, the diode behaves like a conductor. The forward voltage beyond which the current through the junction starts increasing rapidly with voltage is called knee voltage. If line AB is extended back, it cuts the voltage axis at potential barrier voltage.

#### (b) Reverse Biased Characteristics

The circuit diagram for studying reverse biased characteristics is shown in the figure.

In reverse biased, the applied voltage supports the flow of minority charge carriers across the junction. So, a very small current flows across the junction due to minority charge carriers. Motion of minority charge carriers is also supported by internal potential barrier, so all the minority carriers cross over the junction. Therefore, the small reverse current remains almost constant over a sufficiently long range of reverse bias, increasing very little with increasing voltage (OC portion of the graph). This reverse current is voltage independent upto certain voltage known as **breakdown voltage** and this voltage independent current – is called reverse saturation current.

#### Use of p-n Junction Characteristics in Rectification

From forward and reverse characteristics, it is clear that current flows through the junction diode only in forward bias not in reverse bias i.e. current flows only in one direction (b)Circuit diagram of illuminated photo diode in reverse bias is shown below:

A reverse biased photodiode

a photodiode

Hence, frequency of light v such that  $hv > E_g$ , where  $E_g$  is band gap of increasing intensity  $l_1, l_2, l_3$ , etc. The value of reverse saturation current increases with the increase of intensity of light.

Thus, the measurement of charge in the reverse saturation current can give the intensity of incident light. (1)

46.(a) Explain with the help of diagram, how a depletion layer and barrier potential are formed in a junction diode.

(b) Draw a circuit diagram of a full-wave rectifier. Explain its working and draw input and output waveforms. [Delhi 2014 c]

Ans.(a)

During formation of p-n junction, diffusion of charge takes place. As, soon as p-type semiconductor is joined with n-type semiconductor, diffusion of free charges across the junction starts.

#### For explanation of formation p-n junction

With the formation of p-n junction, the holes from p-region diffuse into the n-region and electrons from n-region diffuse into p-region and electron-hole pair combine and get annihilated.

This input produces potential barrier,  $V_B$  across in junction which opposes the further diffusion through the junction. Thus, small region forms in the vicinity of the junction which is depleted of free charge carrier and has only immotile ions is called the depletion region.

Potential barrier The potential distribution near the p-n junction is known as potential barrier **(b)**

In these type of questions, we have to mind that in full-wave rectifier, full cycle of the input will be used.

The circuit diagram of full-wave rectifier is shown below:

The input and output waveforms have been given below:

Its working based on the principle that junction diode offer very low resistance in forward bias and very high resistance in reverse bias. (1)

## 47.(i) How is a depletion region formed in p-n junction?(ii)With the help of a labelled circuit diagram. Explain how a junction diode is used as a full-wave rectifier. Draw its input, output wave forms.

#### (iii)How do you obtain steady DC output from the pulsating voltage?[Delhi 2013 C]

**Ans.(i) p-n Junction** A p-n junction is an arrangement made by a close contact of n-type semiconductor and p-type semiconductor. There are various methods of forming p-n junction diode. In one method, an n-type germanium crystal is cut into thin slices called wafers. An aluminium film is laid on an n-type wafer which is then heated in an oven at a temperature of about 600°C. Aluminium then diffuses into the surface of wafer. In this way, a p-type semiconductor is formed on n-type semiconductor.

**Formation of Depletion Region in p-n Junction** In an n-type semiconductor, the concentration of electrons is more than concentration of holes. Similarly, in a p-type semiconductor, the concentration of holes is more than that of concentration of electrons. During formation of p-n junction and due to the concentration gradient across p and n-sides, holes diffuse from p-side to n-side (p-> n) and electrons diffuse from n-side to p-side (n -> p).

The diffused charge carriers combine with their counterparts in the immediate vicinity of the junction and neutralise each other, (I) Thus, near the junction, positive charge is built on n-side and negative charge on p-side This sets up potential difference across the junction and an internal electric field Ej directed from n-side to p-side. The equilibrium is established when the field £, becomes strong enough to stop further diffusion of the majority charge carriers (however, it helps the minority charge carriers to diffuse across the junction). The region on either side of the junction which becomes depleted (free) from the mobile charge carriers is called depletion region or **depletion layer**. The width of depletion region is of the order of  $10^{-6}$  m. The potential difference developed across the depletion region is called the potential barrier. Potential barrier depends on dopant concentration in the semiconductor and temperature of the junction.

In these type of questions, we have to mind that in full-wave rectifier, full cycle of the input will be used.

The circuit diagram of full-wave rectifier is shown below:

The input and output waveforms have been given below:

Its working based on the principle that junction diode offer very low resistance in forward bias and very high resistance in reverse bias. (1)

(iii) A full-wave bridge rectifier using four diodes (full-wave bridge rectifier) gives a continuous, unidirectional but pulsating output voltage or current.

The rectified output is passed through a filter circuit which removes the ripple and an almost steady DC voltage (or current) is obtained.

48.Why is a Zener diode considered as a special purpose semiconductor diode? Draw the I-V characteristics of Zener diode and explain briefly, how reverse current suddenly

## increase at the breakdown voltage? Describe briefly with the help of a circuit diagram, how a Zener diode work's to obtain a constant DC voltage from the unregulated DC output of a rectifier.[Delhi 2009 C; Foreign 2012]

**Ans.**Zener diode works only in reverse breakdown region that is why it is considered as a special purpose semiconductor

### *I-V* characteristics of Zener diode is given below: (1) Reverse bias $V_z$ $V_z$ V(V)I (mA)

Reverse current is due to the flow of electrons from n  $\rightarrow$  p and holes from p  $\rightarrow$  n. As, the reverse biased voltage increase the elecHic field across the junction, increases signiffcantly and when reverse bias voltage V – V<sub>z</sub>, then the electric field strength is high enough to pull the electrons from p-side and accelerated it to n-side.

These electrons are responsible for the high current at the breakdown.

Voltage regulator converts an unregulated DC output of rectifier into a constant regulated DC voltage, using Zener diode. The unregulated voltage is connected to the Zener diode through a series resistance  $R_s$  such that the Zener diode is reverse biased. If the input voltage increases, then current through  $R_s$  apd Zener diode increases. Thus, the voltage drop across  $R^{A}$  increases without any change in the voltage drop across Zener diode. This is because of the breakdown region, Zener voltage remain constant even though the current through Zener diode changes.

Similarly, if the input voltage decreases, the current through  ${\sf R}_{s}$  and Zener diode decreases. The voltage drop across  ${\sf R}_{s}$ , decreases without any change in the voltage across the Zener diode.

Now, any change in input voltage results the change in voltage drop across  $\mathsf{R}_{\mathsf{s}}$ , without any change in voltage across the Zener diode. Thus, Zener diode acts as a voltage regulator

## 49.(i) Describe briefly, with the help of a diagram, the role of the two important processes involved in the formation of a p-n junction.

(ii) Name the device which is used as a voltage regulator. Draw the necessary circuit diagram and explain its working.[HOTS; All India 2012]

Ans.

When we are dealing with depletion layer formation we have to keep in mind the majority charge carriers, diffusion will always happens from high concentration to low concentration.

The two process involved in the formation of p-n junction.

(a)Diffusion

(b)Drift

Holes and electrons diffuse from p to n and n to p respectively.

The majority charge carrier drifts under the influence of applied electric field such that

(a)holes along applied E and

(b)electron opposite to E.

(ii) Zener diode is used as voltage regulator.

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

50.(i) Draw the circuit diagram of a p-n junction diode in

(a)forward bias.

(b)reverse bias.

How are these circuits used to study the V-1 characteristics of a silicon diode? Draw the typical V-I characteristics.

(ii) What is a Light Emitting Diode (LED)? Mention two important advantage of LEDs over conventional lamps.[Delhi 2010 C; All India 2010]

**Ans.(i) p-n Junction** A p-n junction is an arrangement made by a close contact of n-type semiconductor and p-type semiconductor. There are various methods of forming p-n junction diode. In one method, an n-type germanium crystal is cut into thin slices called wafers. An aluminium film is laid on an n-type wafer which is then heated in an oven at a temperature of about 600°C. Aluminium then diffuses into the surface of wafer. In this way, a p-type semiconductor is formed on n-type semiconductor.

Formation of Depletion Region in p-n Junction In an n-type semiconductor, the

concentration of electrons is more than concentration of holes. Similarly, in a p-type semiconductor, the concentration of holes is more than that of concentration of electrons. During formation of p-n junction and due to the concentration gradient across p and n-sides, holes diffuse from p-side to n-side (p-> n) and electrons diffuse from n-side to p-side (n -> p).

The diffused charge carriers combine with their counterparts in the immediate vicinity of the junction and neutralise each other, (I) Thus, near the junction, positive charge is built on n-side and negative charge on p-side This sets up potential difference across the junction and an internal electric field Ej directed from n-side to p-side. The equilibrium is established when the field £, becomes strong enough to stop further diffusion of the majority charge carriers (however, it helps the minority charge carriers to diffuse across the junction). The region on either side of the junction which becomes depleted (free) from the mobile charge carriers is called depletion region or **depletion layer**. The width of depletion region is of the order of 10<sup>-6</sup> m. The potential difference developed across the depletion region is called the potential barrier. Potential barrier depends on dopant concentration in the semiconductor and temperature of the junction.

#### (a) Forward Biased Characteristics

The circuit diagram for studying forward biased characteristics is shown in the figure. Starting from a low value, forward bias voltage is increased step by step (measured by voltmeter) and forward current is noted (by ammeter). A graph is plotted between voltage and current. The curve so obtained is the forward characteristic of the diode.

because of the potential barrier, which opposes the applied voltage. Till the applied voltage exceeds the potential barrier, the current increases very slowly with increase in applied voltage (OA portion of the graph). With further increase in applied voltage, the current increases very rapidly (AB portion of the graph), in this situation, the diode behaves like a conductor. The forward voltage beyond which the current through the junction starts increasing rapidly with voltage is called knee voltage. If line AB is extended back, it cuts the voltage axis at potential barrier voltage.

#### (b) Reverse Biased Characteristics

The circuit diagram for studying reverse biased characteristics is shown in the figure.

In reverse biased, the applied voltage supports the flow of minority charge carriers across the junction. So, a very small current flows across the junction due to minority charge carriers. Motion of minority charge carriers is also supported by internal potential barrier, so all the minority carriers cross over the junction. Therefore, the small reverse current remains almost constant over a sufficiently long range of reverse bias, increasing very little with increasing voltage (OC portion of the graph). This reverse current is voltage independent upto certain voltage known as **breakdown voltage** and this voltage independent current – is called reverse saturation current.

#### Use of p-n Junction Characteristics in Rectification

From forward and reverse characteristics, it is clear that current flows through the junction diode only in forward bias not in reverse bias i.e. current flows only in one direction **(ii)** (a) Working of LED LED is a forward biased p-n junction which converts electrical energy into optical energy of infrared and visible light region.

Being in forward bias, thin depletion layer and low potential barrier facilitate diffusion of electron and hole through the junction when high energy electron of conduction band combines with the low energy holes in valence band, then energy is released in the form of photon, may be seen in the form of light.

(b)Uses of LEDs (a) LED can operate at very low voltage and consumes less power in comparison to incandescent lamps. Unlike the lamps, they take very less operational time and have long life.

#### 51.(i) Draw I-V characteristics of a Zener diode.

(ii)Explain with the help of a circuit diagram, the use of a Zener diode as a voltage regulator.

(iii)A photo diode is operated under reverse bias although in the forward bias, the current is known to be more than the current in the reverse bias. Explain, giving reason. [HOTS; Foreign 2010]

$\label{eq:Ans.} \textbf{(i)} Zener \ diode \ is \ used \ as \ voltage \ regulator.$

**Principle** Zener diode is operated in the reverse breakdown region. The voltage across it remains constant, equal to the breakdown voltage for large charge in reverse current

Characteristic of a Zener diode

(ii) From the figure, it is clear that the device, X is a full-wave rectifier. Circuit diagram as shown in figure below:

Zener diode connected with unregulated DC voltage in reverse bias. When the input voltage increases, then current through R, increase and hence, voltage drop across  $R_p$  increases while voltage across the Zener diode remains constant. The voltage across Zener diode remains constant beyond Zener voltage and hence, same/constant regulated voltage is obtained across  $R_L$ .

(iii) In n-type semiconductor,

$n_e > n_h$  ...(i) On incidence of light of suitable frequency, there is equal rise in number of electrons and holes [i.e.  $\Delta n$  (say)]  $\Rightarrow \qquad \frac{1}{n_e} < \frac{1}{n_h} \text{ or } \frac{\Delta n}{n_e} < \frac{\Delta n}{n_h}$ where,  $\Delta n$  = change in electron or hole charge carrier.

Thus, fractional change in minority charge carrier (hole) is much higher than fraction change in majority charge carrier (electron). Also, minority charge carrier contribute in drift current in reverse bias.

Thus, with incidence of light, fractional change in minority charge carrier is significant. Therefore, photo diode should be connected in reverse bias for measuring light intensity.

52.(i) Draw a circuit arrangement for studying V-I characteristics of a p-n junction diode in(a) forward bias and (b) reverse bias.

Show typical V-I characteristics of a silicon diode.

(ii) State the main practical application of LED. Explain, giving reason, why the semiconductor used for

fabrication of visible light LEDs must have a band gap of at least (nearly) 1.8 eV. [Delhi 2010 C]

**Ans.(i) p-n Junction** A p-n junction is an arrangement made by a close contact of n-type semiconductor and p-type semiconductor. There are various methods of forming p-n junction

diode. In one method, an n-type germanium crystal is cut into thin slices called wafers. An aluminium film is laid on an n-type wafer which is then heated in an oven at a temperature of about 600°C. Aluminium then diffuses into the surface of wafer. In this way, a p-type semiconductor is formed on n-type semiconductor.

**Formation of Depletion Region in p-n Junction** In an n-type semiconductor, the concentration of electrons is more than concentration of holes. Similarly, in a p-type semiconductor, the concentration of holes is more than that of concentration of electrons. During formation of p-n junction and due to the concentration gradient across p and n-sides, holes diffuse from p-side to n-side (p->n) and electrons diffuse from n-side to p-side (n -> p).

The diffused charge carriers combine with their counterparts in the immediate vicinity of the junction and neutralise each other, (I) Thus, near the junction, positive charge is built on n-side and negative charge on p-side This sets up potential difference across the junction and an internal electric field Ej directed from n-side to p-side. The equilibrium is established when the field £, becomes strong enough to stop further diffusion of the majority charge carriers (however, it helps the minority charge carriers to diffuse across the junction). The region on either side of the junction which becomes depleted (free) from the mobile charge carriers is called depletion region or **depletion layer**. The width of depletion region is of the order of 10<sup>-6</sup> m. The potential difference developed across the depletion region is called the potential barrier. Potential barrier depends on dopant concentration in the semiconductor and temperature of the junction.

#### (a) Forward Biased Characteristics

The circuit diagram for studying forward biased characteristics is shown in the figure. Starting from a low value, forward bias voltage is increased step by step (measured by voltmeter) and forward current is noted (by ammeter). A graph is plotted between voltage and current. The curve so obtained is the forward characteristic of the diode.

At the start when applied voltage is low, the current through the diode is almost zero. It is because of the potential barrier, which opposes the applied voltage. Till the applied voltage exceeds the potential barrier, the current increases very slowly with increase in applied voltage (OA portion of the graph). With further increase in applied voltage, the current increases very rapidly (AB portion of the graph), in this situation, the diode behaves like a conductor. The forward voltage beyond which the current through the junction starts increasing rapidly with voltage is called knee voltage. If line AB is extended back, it cuts the voltage axis at potential barrier voltage.

#### (b) Reverse Biased Characteristics

The circuit diagram for studying reverse biased characteristics is shown in the figure.

In reverse biased, the applied voltage supports the flow of minority charge carriers across the junction. So, a very small current flows across the junction due to minority charge carriers. Motion of minority charge carriers is also supported by internal potential barrier, so all the minority carriers cross over the junction. Therefore, the small reverse current remains almost constant over a sufficiently long range of reverse bias, increasing very little with increasing voltage (OC portion of the graph). This reverse current is voltage independent upto certain voltage known as **breakdown voltage** and this voltage independent current – is called reverse

saturation current.

#### Use of p-n Junction Characteristics in Rectification

From forward and reverse characteristics, it is clear that current flows through the junction diode only in forward bias not in reverse bias i.e. current flows only in one direction **(ii)** Working of LED LED is a forward biased p-n junction which converts electrical energy into optical energy of infrared and visible light region.

Being in forward bias, thin depletion layer and low potential barrier facilitate diffusion of electron and hole through the junction when high energy electron of conduction band combines with the low energy holes in valence band, then energy is released in the form of photon, may be seen in the form of light.

(a) Semiconductors with appropriate band gap ( $E_g$ ) close to 1.5 eV are preferred to make LED size GaAs, CdTe, etc.the other reasons to select these materials e high optical absorption, availability of raw material and low cost

(b) Uses of LEDs

(i) LED can operate at very low voltage and consumes less power in comparison to incandescent lamps

(ii) Unlike the lamps, they take very less operational time and have long life.

# 53. How is a Zener diode fabricated so as to make it a special purpose diode? Draw 7-V characteristics of Zener diode and explain the significance of breakdown voltage, (ii) Explain briefly, with the help of a circuit diagram, how a p-n junction diode works as a half-wave rectifier. [Delhi 2009c]

**Ans.(i)**Zener diode works only in reverse breakdown region that is why it is considered as a special purpose semiconductor

Reverse current is due to the flow of electrons from n  $\rightarrow$  p and holes from p  $\rightarrow$  n. As, the reverse biased voltage increase the elecHic field across the junction, increases signiffcantly and when reverse bias voltage V – V<sub>z</sub>, then the electric field strength is high enough to pull the electrons from p-side and accelerated it to n-side.

These electrons are responsible for the high current at the breakdown.

Voltage regulator converts an unregulated DC output of rectifier into a constant regulated DC voltage, using Zener diode. The unregulated voltage is connected to the Zener diode through a series resistance  $R_s$  such that the Zener diode is reverse biased. If the input voltage increases, then current through  $R_s$  apd Zener diode increases. Thus, the voltage drop across  $R^{-1}$

increases without any change in the voltage drop across Zener diode. This is because of the breakdown region, Zener voltage remain constant even though the current through Zener diode changes.

Similarly, if the input voltage decreases, the current through  $R_s$  and Zener diode decreases. The voltage drop across  $R_s$ , decreases without any change in the voltage across the Zener diode.

Now, any change in input voltage results the change in voltage drop across R<sub>s</sub>, without any change in voltage across the Zener diode. Thus, Zener diode acts as a voltage regulator (ii) Circuit diagram of p-n junction diode as half-wave rectifier is shown below

Diode conducts corresponding to positive half cycle and does not conduct during negative half cycle hence, AC is converted by diode into unidirectional pulsating DC. This action is known as half-wave rectification.

54.(i) Draw the typical shape of the V-I characteristics of a p-n junction diode both in (a) forward(b)reverse bias configuration. How do we infer, from these characteristics that a diode can be used to rectify alternating voltages?

(ii) Draw the circuit diagram of a full-wave rectifier using a centre-tap transformer and two p-n junction diodes. Give a brief description of the working of this circuit. [Delhi 2009 C]

**Ans.(i) p-n Junction** A p-n junction is an arrangement made by a close contact of n-type semiconductor and p-type semiconductor. There are various methods of forming p-n junction diode. In one method, an n-type germanium crystal is cut into thin slices called wafers. An aluminium film is laid on an n-type wafer which is then heated in an oven at a temperature of about 600°C. Aluminium then diffuses into the surface of wafer. In this way, a p-type semiconductor is formed on n-type semiconductor.

**Formation of Depletion Region in p-n Junction** In an n-type semiconductor, the concentration of electrons is more than concentration of holes. Similarly, in a p-type semiconductor, the concentration of holes is more than that of concentration of electrons. During formation of p-n junction and due to the concentration gradient across p and n-sides, holes diffuse from p-side to n-side (p-> n) and electrons diffuse from n-side to p-side (n -> p).

The diffused charge carriers combine with their counterparts in the immediate vicinity of the junction and neutralise each other, (I) Thus, near the junction, positive charge is built on n-side and negative charge on p-side This sets up potential difference across the junction and an internal electric field Ej directed from n-side to p-side. The equilibrium is established when the field £, becomes strong enough to stop further diffusion of the majority charge carriers (however, it helps the minority charge carriers to diffuse across the junction). The region on either side of the junction which becomes depleted (free) from the mobile charge carriers is called depletion region or **depletion layer**. The width of depletion region is of the order of 10<sup>-6</sup> m. The potential difference developed across the depletion region is called the potential barrier. Potential barrier depends on dopant concentration in the semiconductor and temperature of the junction.

#### (a) Forward Biased Characteristics

The circuit diagram for studying forward biased characteristics is shown in the figure. Starting from a low value, forward bias voltage is increased step by step (measured by voltmeter) and forward current is noted (by ammeter). A graph is plotted between voltage and current. The curve so obtained is the forward characteristic of the diode.

At the start when applied voltage is low, the current through the diode is almost zero. It is because of the potential barrier, which opposes the applied voltage. Till the applied voltage exceeds the potential barrier, the current increases very slowly with increase in applied voltage (OA portion of the graph). With further increase in applied voltage, the current increases very rapidly (AB portion of the graph), in this situation, the diode behaves like a conductor. The forward voltage beyond which the current through the junction starts increasing rapidly with

voltage is called knee voltage. If line AB is extended back, it cuts the voltage axis at potential barrier voltage.

#### (b) Reverse Biased Characteristics

The circuit diagram for studying reverse biased characteristics is shown in the figure.

In reverse biased, the applied voltage supports the flow of minority charge carriers across the junction. So, a very small current flows across the junction due to minority charge carriers. Motion of minority charge carriers is also supported by internal potential barrier, so all the minority carriers cross over the junction. Therefore, the small reverse current remains almost constant over a sufficiently long range of reverse bias, increasing very little with increasing voltage (OC portion of the graph). This reverse current is voltage independent upto certain voltage known as **breakdown voltage** and this voltage independent current – is called reverse saturation current.

#### Use of p-n Junction Characteristics in Rectification

From forward and reverse characteristics, it is clear that current flows through the junction diode only in forward bias not in reverse bias i.e. current flows only in one direction

(ii)

In these type of questions, we have to mind that in full-wave rectifier, full cycle of the input will be used.

The circuit diagram of full-wave rectifier is shown below:

The input and output waveforms have been given below:

Its working based on the principle that junction diode offer very low resistance in forward bias and very high resistance in reverse bias. (1)

# LogicGates, Transistors and its Applications

# **1 Mark Questions**

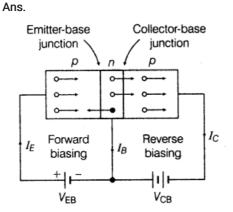

1.In a transistor, doping level in base is increased slightly. How will it affect

(i)collector current and

(ii)base current? [Delhi 2011]

Ans.(i) Collector current decreases.

(ii) Base current increases

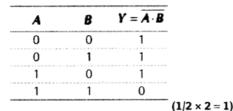

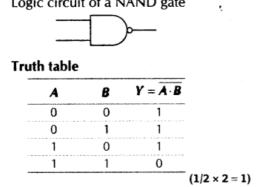

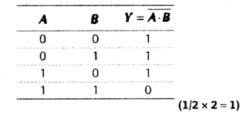

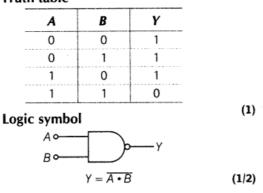

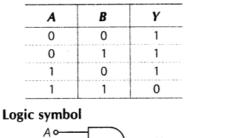

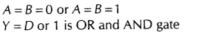

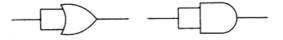

2.Draw the logic circuit of a NAND gate and write its truth table.[Foreign 20113] Ans.

,

Logic circuit of a NAND gate

Truth table

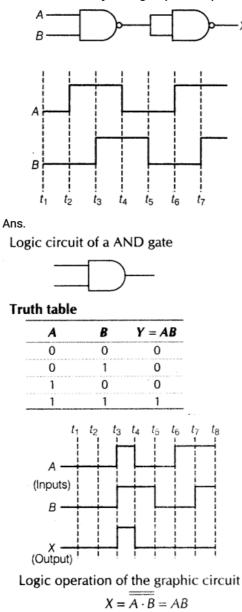

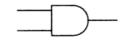

3.Draw the logic circuit of AND gate and write its truth table.[Foreign 2011] Ans.

Logic circuit of a AND gate

Truth table

| Α | B | Y = AB |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

4.Draw the logic circuit of NOT gate and write its truth table.[Foreign 2011] Ans.

Logic circuit of a NOT gate

Truth table

| Α | $Y = \overline{A}$ |

|---|--------------------|

| 0 | 1                  |

| 1 | 0                  |

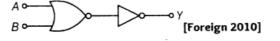

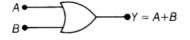

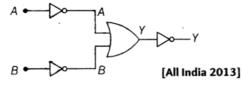

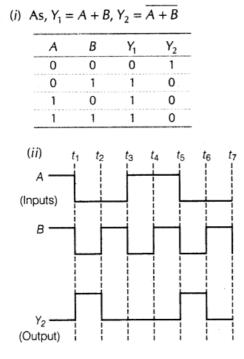

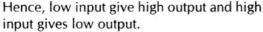

**5.** Write the truth table for the following circuit. Name the equivalent gate that this circuit represents.

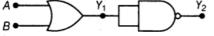

The given combination consists of NOR gate and NOT gate, so equivalent gate is OR gate. **Truth table**

| Α | B | Y = A + B |

|---|---|-----------|

| 0 | 0 | 0         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 1         |

$(1/2 \times 2 = 1)$

From the truth table, it is clear that the output is 1 only when at least one of the inputs is at the high state i.e. 1

6. The truth table of a logic gate has the form given here. Name this gate and draw its symbol.

|   |   | [All India 2010C] |

|---|---|-------------------|

| 1 | 1 | 0                 |

| 1 | 0 | 0                 |

| 0 | 1 | 0                 |

| 0 | 0 | 1                 |

| Α | B | Y                 |

|   |   |                   |

Ans.

Logic gate is NOR gate.

#### Symbol

7. The truth table of a logic gate has the form given here. Name this gate and draw its symbol.

| A | B | Ŷ                 |

|---|---|-------------------|

| 0 | 0 | 1                 |

| 0 | 1 | 1                 |

| 1 | 0 | 1                 |

| 1 | 1 | 0                 |

|   |   | [All India 2010C] |

Ans.

Logic circuit of a NAND gate

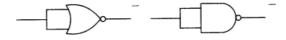

8. Give the logic symbol of NOR gate. [All India 2009] Ans.

Logic gate is NOR gate. Symbol

$\Box$

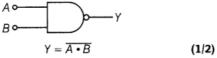

9. Give the logic symbol of NAND gate. [All India 2009] Ans.

t,

Logic circuit of a NAND gate

Truth table

10. Give the logic symbol of AND gate. [All India 2009] Ans.

Logic circuit of a AND gate

Truth table

| Α | B | Y = AB |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

|   |   |        |

11.Define current amplification factor in common-emitter mode of transistor. [Delhi 2009 C, All India 2010 C]

Ans.

Current amplification factor in common emitter mode,  $\beta_{AC} = \left| \frac{\Delta I_C}{\Delta I_B} \right|_{V_{CE} = \text{ constant}}$  (1)

### **2 Marks Questions**

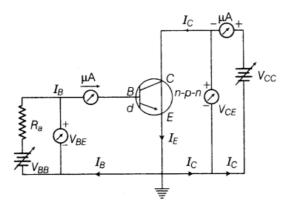

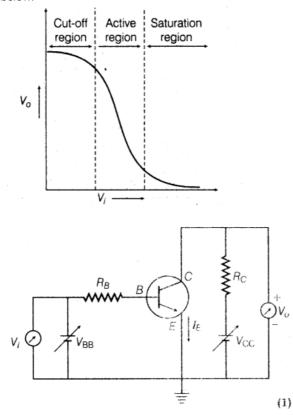

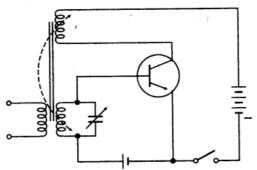

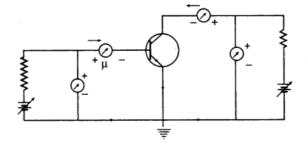

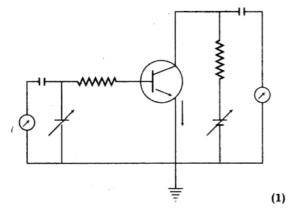

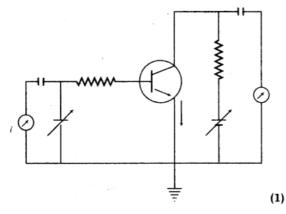

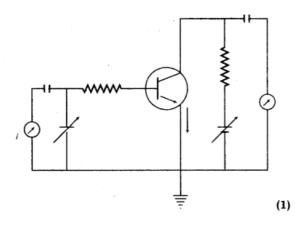

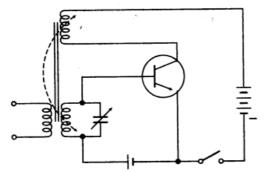

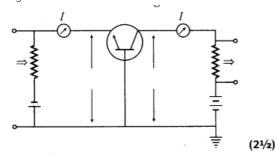

12.Draw a circuit diagram of n-p-n transistor amplifier in CE configuration. Under what condition does the transistor act as an amplifier? [All India 2014]

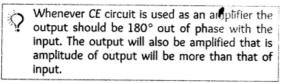

Ans. Circuit diagram of n-p-n transistor amplifier in CE configuration is given below

The condition for the amplifier to work is that the base-emitter junction should be forward biased and collector-base junction should be reversed biased

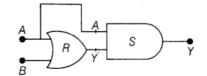

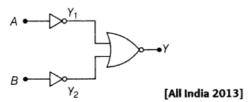

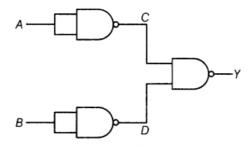

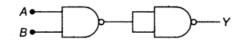

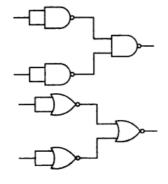

**13.** Write the truth table for the combination of the gates shown. Name the gates used. [All India 2014]

Ans.

| A | B | Y' = A + B | $Y = A \cdot (A + B)$ |

|---|---|------------|-----------------------|

| 0 | 0 | 0          | 0                     |

| 0 | 1 | 1          | 0                     |

| 1 | 0 | 1          | 1                     |

| 1 | 1 | 1          | 1                     |

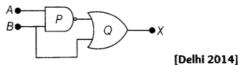

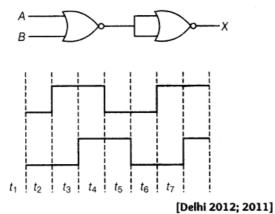

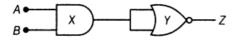

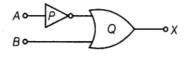

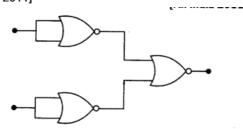

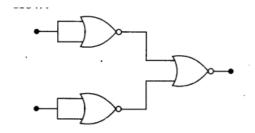

**14.** Identify the logic gates marked *P* and *Q* in the given circuit. Write the truth table for the combination.

#### Ans.

The logic gates are Pis NAND gate and Q is OR gate. The truth table is given as shown in below:

| A | B |   |   | $\boldsymbol{X} = \boldsymbol{B} + \overline{\boldsymbol{A} \cdot \boldsymbol{B}}$ |

|---|---|---|---|------------------------------------------------------------------------------------|

| 0 | 0 | 0 | 1 | 1                                                                                  |

| 0 | 1 | 0 | 1 | 1                                                                                  |

| 1 | 0 | 0 | 1 | 1                                                                                  |

| 1 | 1 | 1 | 0 | 1                                                                                  |

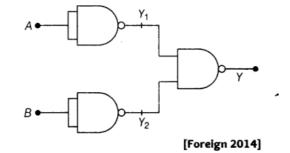

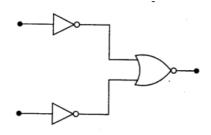

15. The outputs of two NOT gates are fed to a NOR gate. Draw the logic circuit of the combination of gates. Give its truth table. Identify the gate represented by this combination. [Delhi 2014 C]

Ans.

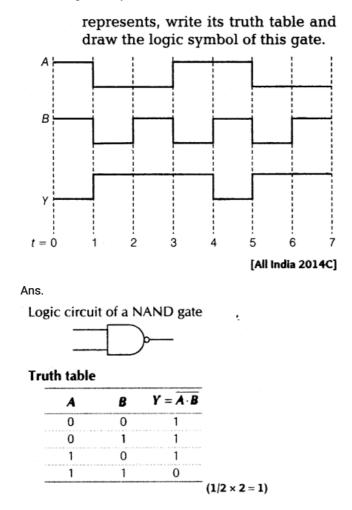

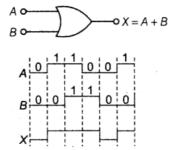

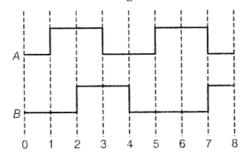

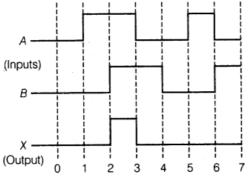

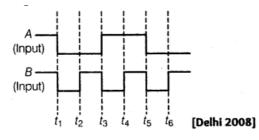

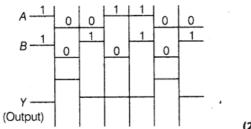

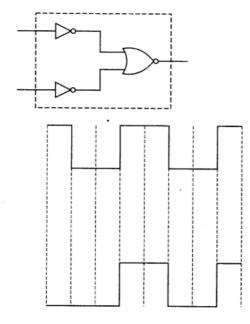

16. The input wave forms A and B and the output waveform Y of a gate are shown below.

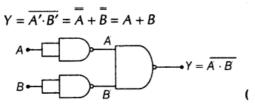

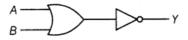

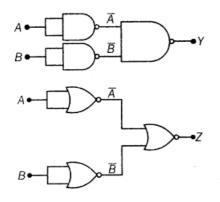

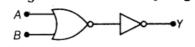

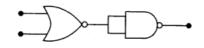

17. Identify the equivalent gate represented by the circuit shown in the figure. Draw its logic symbol and write the truth table.

Ans.

and logic symbol is

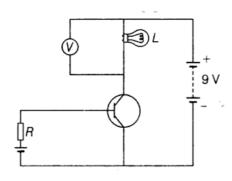

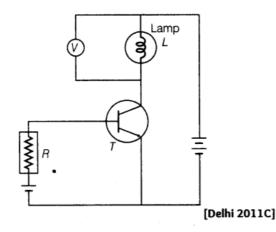

18.In the given circuit diagram, a voltmeter V is connected across a lamp L. How would (i)the brightness of the lamp and

(ii)voltmeter reading V be affected if the value of resistance R is decreased? Justify your answer.

Ans.

The given figure in question is common-emitter (*CE*) configuration of an *n-p-n* transistor. The input circuit is forward biased and collector circuit is reverse biased. (1)

As, the base resistance *R* decreases, the input circuit will become more forward biased thus, decreasing the base current  $(l_B)$  and increasing the emitter current  $(l_C)$ . This will increase the collector current  $(l_C)$  as  $l_E = l_B + l_C$ .

When  $l_C$  increases which flows through the lamp, the voltage across the bulb will also increase thus making the lamp brighter and as the voltmeter is connected in parallel with the lamp, the reading in the voltmeter will also increases. (1)

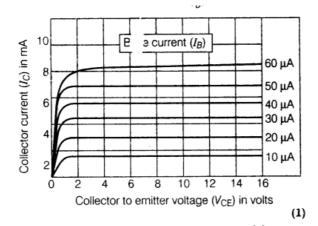

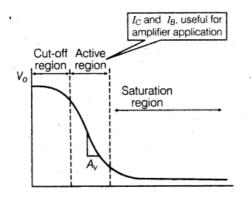

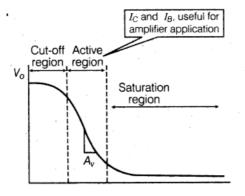

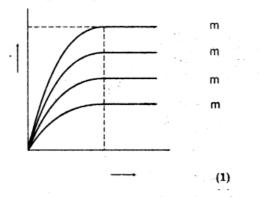

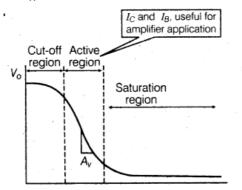

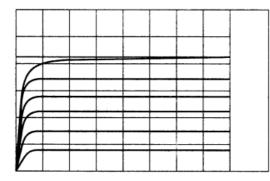

19.Draw a typical output characteristics of an n-p-n transistor in CE Show how these characteristics can be used to determine output resistance?[All India 2013] Ans.

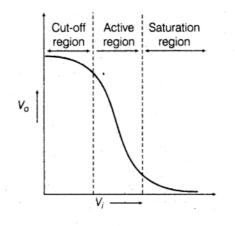

Output characteristics is the plot between collector-emitter voltage ( $V_{CE}$ ) and the collector current ( $l_C$ ) at different constant values of base current ( $l_B$ ).

Output resistance is defined as the ratio of variation of collector-emitter voltage ( $\Delta I_C$ ) and corresponding change in collector current ( $\Delta I_C$ ) when base current remains constant. Initially with the increase in  $V_{CE}$  the collector current increases almost linearly, this is because the junction is not reverse biased. When the supply is more

than required to reverse bias, the base-collector junction,  $i_C$  increases very little with  $V_{CE}$ .

The reciprocal of slope of the linear part of the curve gives the value of output resistance, i.e.  $r_0 = \left(\frac{\Delta V_{CE}}{\Delta I_C}\right) I_{g}$  (1)

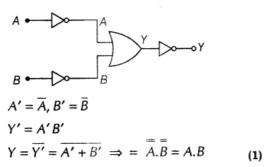

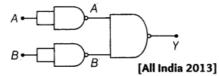

**20.** In the circuit shown in the figure, identify the equivalent gate of the circuit and make its truth table.

Ans.

The equivalent gate of the given circuit is AND gate.

#### Truth table

| A | B | A' | B' | Y' | Y |

|---|---|----|----|----|---|

| 1 | 1 | 0  | 0  | 0  | 1 |